Cuprins:

- Pasul 1: Diagrama bloc

- Pasul 2: Principiul de funcționare

- Pasul 3: Implementarea logicii

- Pasul 4: Rezolvarea blocajului

- Pasul 5: Configurarea dispozitivului - Circuitul Matrix0

- Pasul 6: Configurarea dispozitivului - Logica SPI Clocking

- Pasul 7: Configurarea dispozitivului - Proprietățile componentelor Matrix0

- Pasul 8: Configurarea dispozitivului - Circuitul Matrix1

- Pasul 9: Configurarea dispozitivului - Contor binar pe 3 biți

- Pasul 10: Configurarea dispozitivului - Logică de comparație pe 3 biți

- Pasul 11: Configurarea dispozitivului - Logică de comparație digitală și registru temporar

- Pasul 12: Configurarea dispozitivului - Proprietățile componentelor Matrix1

- Pasul 13: Rezultate

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:42.

- Modificat ultima dată 2025-01-23 15:04.

Sistemele de control și dispozitivele conexe se ocupă de mai multe surse de alimentare, cum ar fi liniile de polarizare sau bateriile și trebuie să urmărească cea mai înaltă (sau cea mai mică) linie dintr-un set dat.

De exemplu, comutarea sarcinii într-un sistem alimentat cu „baterie multiplă” necesită ca sistemul să monitorizeze fie tensiunea minimă, fie cea maximă din gama bateriilor (max sau min în funcție de algoritmul de comutare particular) și direcționează dinamic sarcina către cea mai potrivită sursă în timp real. Alternativ, este posibil ca sistemul să fie nevoit să deconecteze temporar bateria cu cea mai mică tensiune pentru o încărcare corectă.

Un alt exemplu este sistemul modern de energie solară, în care fiecare panou solar este echipat cu un mecanism de înclinare și cu un circuit de urmărire solară (acesta din urmă furnizând informații despre poziția Soarelui pentru a orienta panoul). Cu informațiile despre tensiunea maximă, fiecare poziție a panoului solar poate fi reglată fin pe baza panoului șirului care oferă de fapt cea mai mare tensiune de ieșire, obținându-se astfel un nivel superior de optimizare a puterii.

Există mai multe mărci diferite de IC-uri comerciale (în principal microcontrolere) care, în principiu, pot implementa un adept de tensiune maximă. Cu toate acestea, acestea necesită programare și sunt mai puțin rentabile decât o soluție cu semnal mixt. Completarea unui design Dialog GreenPAK ™ poate afecta pozitiv accesibilitatea, dimensiunea și modularitatea designului. Acest design exploatează avantajul integrării circuitelor analogice și digitale într-un singur cip.

În acest instructabil, sunt implementate front-end-ul analogic și logica digitală necesare pentru a implementa un dispozitiv de căutare a tensiunii maxime (sau eventual minime) între opt surse distincte.

Pentru a implementa monitorul analogic de tensiune max / min pe 8 canale se utilizează un SLG46620G.

Mai jos am descris pașii necesari pentru a înțelege modul în care soluția a fost programată pentru a crea monitorul analogic de tensiune max / min cu 8 canale. Cu toate acestea, dacă doriți doar să obțineți rezultatul programării, descărcați software-ul GreenPAK pentru a vizualiza fișierul de proiectare GreenPAK deja finalizat. Conectați kitul de dezvoltare GreenPAK la computer și apăsați programul pentru a crea monitorul analogic de tensiune max / min cu 8 canale.

Pasul 1: Diagrama bloc

Figura 1 prezintă diagrama globală a sistemului implementat.

Un șir de până la 8 surse de tensiune variabilă este multiplexat și interfațat la modulul ADC al unui GreenPAK conectat la un design intern personalizat capabil să selecteze sursa cu cea mai mare tensiune față de celelalte. Logica internă transmite aceste informații pentru afișare sau procesare ulterioară.

Proiectarea se bazează pe produsul GreenPAK SLG46620G, deoarece încorporează toate blocurile de construcție analogice și digitale necesare pentru aplicație. În această implementare, matricea este scanată cu ajutorul unui multiplexor analog ADG508 acționat direct de GreenPAK IC.

Informațiile de ieșire sunt un număr digital pe 3 biți corespunzător numărului sursei de tensiune la tensiunea maximă. O modalitate directă de a obține aceste informații este de a afișa numărul prin intermediul unui afișaj pe 7 segmente. Poate fi realizat cu ușurință prin interfața ieșirii digitale a SLG46620G cu un driver de afișare pe 7 segmente, cum ar fi soluția GreenPAK descrisă în Referință sau la un IC comun 74LS47.

Circuitul prezentat caută tensiunea maximă. Pentru a converti proiectul într-un dispozitiv de căutare a tensiunii minime, trebuie adăugat un circuit simplu de pre-condiționare între multiplexorul analogic și intrarea analogică GreenPAK, scăzând ieșirea multiplexorului dintr-o tensiune de referință de 1 V.

Pasul 2: Principiul de funcționare

Proiectarea își propune să selecteze sursa cu tensiune maximă, prin urmare se efectuează o scanare pe întreaga matrice în timp ce se stochează ultima valoare maximă și se compară cu următoarea valoare din intrare (care aparține următoarei surse de tensiune din scanare).

În cele ce urmează ne vom referi la o secvență completă de multiplexare de-a lungul tuturor intrărilor ca „scanare” sau „buclă”.

Comparația între două valori nu se realizează prin intermediul componentelor ACMP (cu toate acestea, disponibile în SLG46620G), ci mai degrabă prin modulul DCMP, odată ce valorile sunt respectiv digitalizate. Aceasta este o tehnică avansată și rafinată abordată mai întâi în Referință.

Figura 2 arată cum este structurat SLG46620G pentru acest design.

Semnalul de intrare analogică trece la intrarea ADC prin componenta PGA cu un câștig setat de 1. Diverse setări de câștig sunt, de asemenea, posibile pentru a găsi cea mai bună potrivire cu electronica de condiționare front-end dedicată mapării tensiunilor de intrare la 0-1 V gama modulului GreenPAK ADC.

ADC funcționează în modul cu un singur capăt și convertește semnalul analogic într-un cod digital pe 8 biți, care este apoi transferat în modulul DCMP. Codul digital este, de asemenea, introdus în blocul SPI, configurat ca tampon ADC / FSM, unde un cod digital poate fi stocat și nu se poate schimba până când următorul impuls ajunge la intrarea SPI CLK. Observați că un bloc logic dedicat conduce intrarea SPI CLK. Vom investiga această parte mai târziu, deoarece aceasta este logica „de bază” responsabilă pentru buna funcționare. Un nou cod digital este stocat în modulul SPI numai dacă aparține tensiunii maxime reale de intrare.

Componenta DCMP este utilizată pentru a compara datele ADC curente cu ultimul câștigător (care este ultimul maxim găsit) care este stocat în blocul SPI. Acesta va genera un impuls la ieșirea OUT + atunci când noile date ADC sunt mai mari decât precedentul. Folosim semnalul OUT + pentru a actualiza blocul SPI cu noul câștigător.

Un semnal global de ceas conduce conversiile ADC și sincronizarea generală. Odată efectuată o conversie, semnalele de ieșire INT ale ADC pulsează, coordonate în timp cu ieșirea de date paralele ADC. Folosim ieșirea INT și pentru a incrementa un contor binar de 3 biți, implementat de DFF-uri în Matrix1, care este util din trei motive:

1. Liniile de ieșire a contorului se adresează multiplexorului analog extern, servind astfel următoarea tensiune de intrare la ADC;

2. Numărul este înghețat într-un registru de 3 biți (implementat în Matrix1) pentru a stoca câștigătorul temporar în timpul unei scanări;

3. Numărul este decodat pentru a actualiza un al doilea registru de 3 biți (implementat în Matrix0) după finalizarea scanării.

Pasul 3: Implementarea logicii

Modulul ADC furnizează secvențial date convertite ale tuturor tensiunilor de intrare, una după alta, la nesfârșit. Odată ce multiplexorul este adresat 0b111 (zecimal 7), contorul rulează la 0b000 (zecimal 0) începând astfel o nouă scanare a tensiunilor de intrare.

În timpul scanării, semnalul de ieșire ADC INT este generat atunci când ieșirea de date paralelă este validă. Când acest semnal pulsează, multiplexorul analogic trebuie să treacă la următoarea intrare, furnizând PGA tensiunea corespunzătoare. Prin urmare, ieșirea ADC INT este semnalul de ceas direct al contorului binar de 3 biți din figura 2, al cărui cuvânt de ieșire paralelă de 3 biți se adresează direct multiplexorului analog extern („V select” în figura 1).

Să ne referim acum la un exemplu în care tensiunile de intrare ar trebui să aibă următoarele relații:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Figura 3 reprezintă principalele semnale implicate în mecanismul de decizie maximă.

Deoarece datele sunt în cele din urmă încorporate în registrul tampon SPI sincron cu impulsurile INT, există o fereastră de comparație în care conținutul tampon SPI este comparat cu următorul rezultat de conversie ADC. Acest moment particular are ca rezultat generarea de impulsuri OUT + la ieșirea DCMP. Putem profita de aceste impulsuri pentru a încărca noi valori în registrul tampon SPI.

După cum reiese din linia de date tampon SPI din figura precedentă, registrul SPI conține întotdeauna, timp cu timp, cea mai mare valoare dintre cele 8 intrări și este actualizat numai atunci când o valoare mai mare este detectată de modulul DCMP (referindu-se la DCMP OUT + linia de ieșire a graficului, impulsurile lipsă fac ca V2 să rămână blocat în registru până când este comparat cu V5).

Pasul 4: Rezolvarea blocajului

Dacă logica implementată ar fi exact așa cum s-a descris mai sus, este clar că ne-am ciocni într-o situație de impas: sistemul este capabil să detecteze doar tensiuni mai mari decât cea corespunzătoare celor stocate în registrul tampon SPI.

Acest lucru este valabil și în cazul în care această tensiune ar scădea și apoi o altă intrare, până acum mai mică decât aceasta, devine cea mai mare: nu va fi detectată niciodată. Această situație este mai bine explicată în Figura 4, unde sunt prezente doar 3 tensiuni de intrare de dragul claritate.

În momentul iterației 2, V3 scade și V1 este tensiunea maximă reală. Dar modulul DCMP nu oferă un impuls, deoarece datele stocate în registrul tampon SPI (corespunzător la 0,6 V) este mai mare decât cel corespunzător V1 (0,4 V).

Apoi, sistemul se comportă ca un căutare maximă „absolută” și nu actualizează corect ieșirea.

O modalitate frumoasă de a depăși această problemă este de a forța reîncărcarea datelor în registrul tampon SPI atunci când sistemul finalizează un ciclu complet de interogare a tuturor canalelor.

De fapt, dacă tensiunea la acea intrare este încă cea mai mare, nimic nu se schimbă și controlul continuă în siguranță (referindu-se la Figura 4 de mai sus, acesta este cazul iterațiilor de buclă 0 și 1). Pe de altă parte, dacă tensiunea la acea intrare din întâmplare scade la o valoare mai mică decât o altă intrare, atunci reîncărcarea valorii oferă posibilitatea modulului DCMP de a produce un impuls OUT + atunci când îl compară cu noua valoare maximă (aceasta este cazul iterațiilor de buclă 2 și 3).

O bucată de circuit logic este necesară pentru a depăși problema. Trebuie să genereze un semnal de ceas către componenta SPI atunci când bucla atinge intrarea maximă reală, forțând astfel o reîncărcare a cuvântului său de date actualizat în Registrul tampon SPI. Acest lucru va fi discutat în secțiunile 7.2 și 7.6 de mai jos.

Pasul 5: Configurarea dispozitivului - Circuitul Matrix0

SLG46620G are două blocuri Matrix, așa cum este descris în Figura 2. Următoarele figuri prezintă configurațiile dispozitivului respectiv.

Porțiunea superioară a circuitului este „Loop Register” realizat cu 3 DFF (DFF0, DFF1 și DFF2). Se reîmprospătează după fiecare buclă a multiplexorului de intrare pentru a trimite către un driver de afișare pe 7 segmente numărul binar al „câștigătorului”, adică intrarea cu cea mai mare tensiune din ultima scanare. Atât ceasul către DFF-uri, cât și datele provin din logica implementată în Matrix1 prin respectivul port P12, P13, P14 și P15.

Partea inferioară este partea frontală analogică cu intrare la pinul 8 și PGA cu câștig x1. Ieșirea ADC INT merge atât către logica SPI, cât și către Matrix1 prin portul P0, unde va servi ca semnal de ceas pentru contorul implementat.

Ieșirile de date paralele ADC și SPI sunt etichetate respectiv NET11 și NET15 pentru a fi conectate la componenta DCMP din Matrix1.

Pasul 6: Configurarea dispozitivului - Logica SPI Clocking

După cum sa menționat anterior în secțiunea „Implementare logică”, registrul tampon SPI este actualizat de fiecare dată când o comparație între valoarea reală stocată și noile date de conversie ADC generează un impuls la ieșirea DCMP OUT +.

Integritatea semnalului este asigurată dacă acest semnal este AND-ed cu ieșirea ADC INT. Acest lucru evită orice declanșare falsă și falsă.

Am subliniat, de asemenea, că pentru a omite situațiile de blocare, tamponul SPI trebuie actualizat atunci când bucla ajunge la datele reale ale câștigătorului.

Trei semnale sunt apoi în joc pentru un ceas SPI corect:

1. Ieșire ADC INT (LUT0-IN1)

2. Ieșire DCMP OUT + (LUT0-IN0 prin portul P10)

3. Numărul este egal cu semnalul de blocare (LUT0-IN2 prin portul P11)

Primele două sunt AND-ed și ambele OR-ed cu cele din urmă în LUT0, a căror implementare este configurată ca în Figura 6.

Pasul 7: Configurarea dispozitivului - Proprietățile componentelor Matrix0

Figurile 7-10 arată ferestrele de proprietate ale componentelor rămase aparținând Matrix0.

Pasul 8: Configurarea dispozitivului - Circuitul Matrix1

Pasul 9: Configurarea dispozitivului - Contor binar pe 3 biți

Partea superioară a circuitului conține elemente logice, în principal un contor binar de 3 biți tactat de ieșirea ADC INT, după cum sa discutat deja. Acest contor este implementat cu o schemă destul de „standard” prezentată în Figura 12.

Acest contor este realizat în designul nostru prin intermediul Flip-Flops DFF9, DFF10, DFF11 și INV1, LUT4, LUT8. Ieșirea DFF9 este LSB, în timp ce DFF11 este MSB așa cum se arată în Figura 13.

LUT4 este configurat ca un XOR în timp ce LUT8 efectuează logica AND-XOR din Figura 12.

Ieșirile de contor merg la trei pini de ieșire digitale pentru a adresa multiplexorul analogic extern.

LUT10 decodează codul contorului atunci când scanarea este finalizată și alimentează un impuls către Matrix0 prin DLY8 și portul P12. Acest lucru se realizează pur și simplu prin AND-ing ieșirile contorului, decodând astfel numărul 7 dec (0b111 binar, sfârșitul buclei).

Pasul 10: Configurarea dispozitivului - Logică de comparație pe 3 biți

Figura 15 prezintă circuitul utilizat pentru a detecta când bucla iterează la adresa curentă „câștigător”. În acest caz, după cum sa discutat deja, un impuls digital ar trebui să forțeze o reîncărcare a rezultatului ADC curent pentru a rezolva o posibilă situație de blocare.

Adresa „câștigător” este stocată în registrul temporar al Matrix1 (vezi mai jos), în timp ce adresa curentă este transmisă de contorul binar.

Porțile XNOR oferă o ieșire adevărată (logică 1 sau „ridicată”) atunci când ambele intrări sunt egale. AND-ing acest semnal pentru toți biții (LUT9) ne dă un impuls atunci când ambele coduri binare sunt aceleași. Detalii despre porțile XOR ca verificator de paritate pot fi găsite în Referință.

Semnalul „Counter-equal-Latch” este transmis către Matrix0 prin portul P11.

Pasul 11: Configurarea dispozitivului - Logică de comparație digitală și registru temporar

Partea inferioară a figurii 11 (evidențiată în figura 16) prezintă blocul DCMP, partea decizională a acestui design.

DFF6, 7 și 8 formează un registru pe 3 biți pentru a stoca numărul de intrare temporar „câștigător” în timp ce bucla rulează. Intrarea în Flip-Flops sunt ieșirile de contor binar pe 3 biți, așa cum sunt vizibile în circuitul global Matrix1 din Figura 11, omis aici din motive de claritate.

Ieșirile acestui registru nu pot conduce direct afișajul pe 7 segmente, deoarece valoarea stocată aici se modifică în timpul scanării și ar trebui considerată „validă” doar la sfârșitul scanării.

Din acest motiv, ieșirile de registru temporar se conectează la Matrix0’s Loop Register prin porturile inter-matrice P13, P14 și P15.

Este important de observat în Figura 16 că registrul temporar este ceasut de ieșirea DCMP OUT + atunci când ADC-SPI înregistrează comparație rezultând un nou maxim găsit.

Același semnal OUT + este trecut către Matrix0, SPI CLK Logic, prin portul P10.

Pasul 12: Configurarea dispozitivului - Proprietățile componentelor Matrix1

Figurile 17-19 arată ferestrele proprietății componentelor aparținând Matrix1.

Pasul 13: Rezultate

Pentru a testa implementarea, a fost construit un prototip al plăcii de evaluare, unde cele 8 tensiuni analogice de intrare sunt obținute printr-o serie de divizoare de rezistență cu TrimPots (așa cum se arată în Figura 20).

Multiplexorul utilizat este un ADG508, o piesă care poate funcționa cu o singură alimentare (12 V).

Driverul de afișare pe 7 segmente este un 74LS47. Decodează un cuvânt de intrare paralel și conduce direct un afișaj cu 7 segmente cu anod comun.

Placa de evaluare are un conector unghi drept 2x10 pentru a se conecta direct la o platformă de dezvoltare avansată GreenPAK la conectorul său de expansiune, așa cum se arată în Figura 21.

Îmbinarea cu platforma de dezvoltare avansată GreenPAK face foarte simplă măsurarea semnalelor pentru o verificare rapidă. De exemplu, Figura 22 prezintă un set de semnale (respectiv IEȘIRE, ieșire ADC INT și ieșire DCMP OUT +) captate de un analizor logic HP 54620A. Formele de undă sunt declanșate de o margine ascendentă a semnalului OUT + (pe obiectivul etichetat ca „A> B”), prin urmare aceasta este o captură a formei de undă atunci când este detectată o nouă tensiune maximă între intrările analogice. De fapt, a fost obținut prin rotirea unuia dintre TrimPots-urile de pe placa de evaluare pentru a crește tensiunea corespunzătoare prezentată în Figura 22.

Figura 23 prezintă schema Comitetului de evaluare.

Concluzie

În acest instructabil, am implementat un dispozitiv de căutare a tensiunii maxime (sau minime) cu opt canale pentru a fi folosit ca o adăugare obișnuită la sistemele de control multicanal. Abordarea prezentată exploatează caracteristicile avansate ale componentelor GreenPAK și arată cum este posibil să se integreze într-un singur cip funcții analogice și digitale. Mai multe IC comerciale pot fi înlocuite cu Dialog GreenPAK, astfel încât dimensiunea și costul aplicației să poată fi reduse.

Recomandat:

Monitor de tensiune pentru baterii de înaltă tensiune: 3 pași (cu imagini)

Monitor de tensiune pentru baterii de înaltă tensiune: În acest ghid vă voi explica cum mi-am construit monitorul de tensiune al bateriei pentru placa mea electrică. Montați-l cum doriți și conectați doar două fire la baterie (Gnd și Vcc). Acest ghid presupunea că tensiunea bateriei dvs. depășește 30 de volți, w

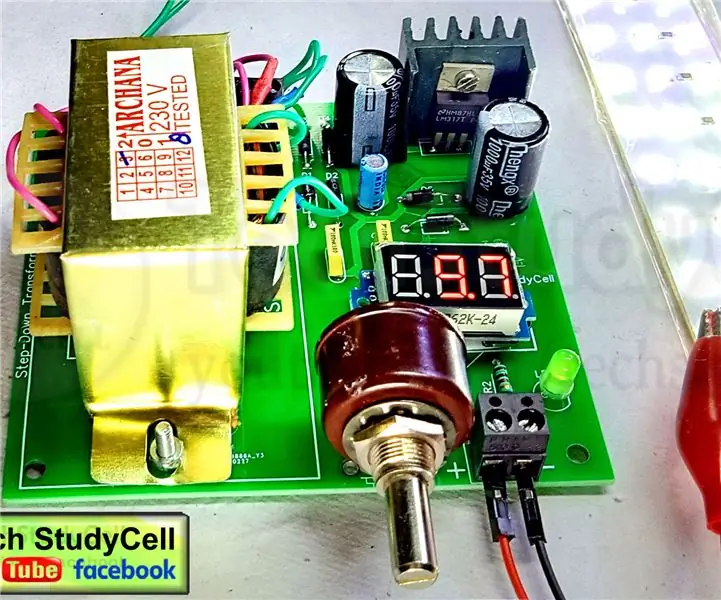

Alimentare de tensiune DC reglabilă utilizând regulatorul de tensiune LM317: 10 pași

Sursa de alimentare DC cu tensiune reglabilă utilizând regulatorul de tensiune LM317: În acest proiect, am proiectat o sursă simplă de alimentare DC cu tensiune reglabilă folosind IC LM317 cu o diagramă a circuitului de alimentare LM317. Deoarece acest circuit are un redresor de punte încorporat, putem conecta direct alimentarea de 220V / 110V AC la intrare

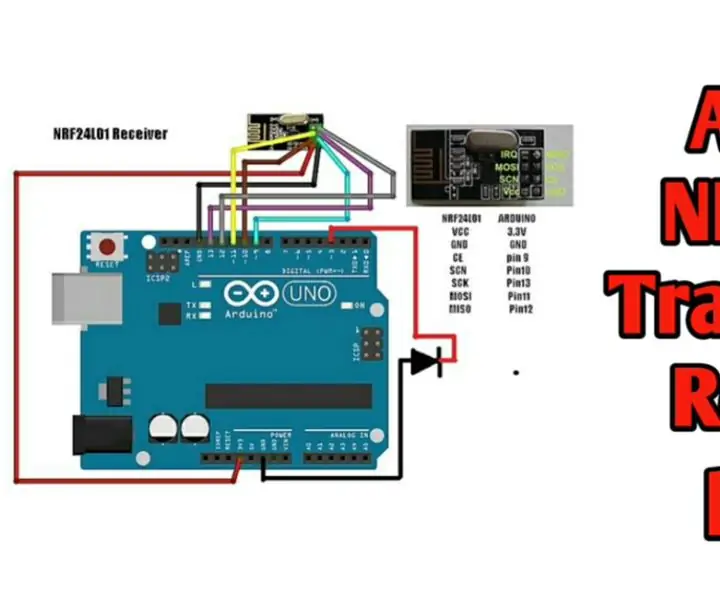

Telecomandă fără fir utilizând modulul NRF24L01 de 2,4 Ghz cu Arduino - Nrf24l01 Receptor transmițător cu 4 canale / 6 canale pentru Quadcopter - Rc Helicopter - Avion Rc folosind

Telecomandă fără fir utilizând modulul NRF24L01 de 2,4 Ghz cu Arduino | Nrf24l01 Receptor transmițător cu 4 canale / 6 canale pentru Quadcopter | Rc Helicopter | Avion Rc folosind Arduino: Pentru a opera o mașină Rc | Quadcopter | Drona | Avion RC | Barcă RC, avem întotdeauna nevoie de un receptor și un transmițător, să presupunem că pentru RC QUADCOPTER avem nevoie de un transmițător și un receptor cu 6 canale, iar acel tip de TX și RX este prea costisitor, așa că vom face unul pe

Amplificator analogic cu 8 canale pentru PC sau HomeTheater: 12 pași (cu imagini)

Amplificator analogic cu 8 canale pentru PC sau HomeTheater: Acesta este primul meu instructable. Vă voi învăța cum să faceți un amplificator cu 8 canale pentru un computer sau un sistem audio cu ieșiri analogice separate, l-am folosit pentru computerul meu de birou, pentru a viziona filme, a asculta muzică HD și a juca jocuri, în plus

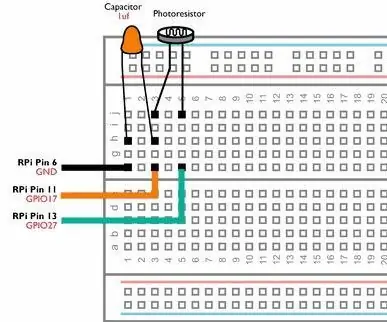

Circuite GPIO Raspberry Pi: Utilizarea unui senzor analogic LDR fără ADC (convertor analogic digital): 4 pași

Circuite GPIO Raspberry Pi: Utilizarea unui senzor analogic LDR fără ADC (convertor analogic la digital): în manualele noastre anterioare, v-am arătat cum puteți conecta pinii GPIO ai Raspberry Pi la LED-uri și comutatoare și modul în care pinii GPIO pot fi mari sau Scăzut. Dar dacă doriți să utilizați Raspberry Pi cu un senzor analogic? Dacă vrem să folosim un