Cuprins:

- Pasul 1: Configurați logica programabilă Zynq pentru emițător

- Pasul 2: Configurați logica programabilă Zynq pentru receptor

- Pasul 3: Configurați driverul VDMA

- Pasul 4: Configurați rețeaua Nanorouter

- Pasul 5: Configurați sistemul de procesare Zynq pentru transmiterea datelor prin Ethernet

- Pasul 6: Configurați sistemul de procesare Zynq pentru recepția datelor prin Ethernet

- Pasul 7: Conectați-vă plăcile Zybo la sursa HDMI și la chiuveta HDMI

- Pasul 8: Idei alternative pentru îmbunătățire

- Pasul 9: Accesibilitate

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:44.

- Modificat ultima dată 2025-01-23 15:04.

V-ați dorit vreodată să vă puteți conecta televizorul la un PC sau laptop ca monitor extern, dar nu ați vrut să aveți toate acele cabluri plictisitoare? Dacă da, acest tutorial este doar pentru dvs.! Deși există unele produse care ating acest obiectiv, un proiect DIY este mult mai satisfăcător și potențial mai ieftin.

Acest concept este diferit de produsele precum chromecastul, deoarece este destinat să înlocuiască un cablu HDMI conectat la un monitor în loc să fie un dispozitiv de streaming.

Proiectul nostru a fost creat ca un proiect final pentru un curs de sisteme de operare în timp real la Universitatea Politehnică de Stat din California, San Luis Obispo.

Scopul proiectului este de a utiliza două plăci Digilent Zybo pentru a acționa ca interfață de comunicație fără fir între un dispozitiv transmițător HDMI (PC, blu-ray etc.) către un dispozitiv de recepție HDMI (monitor desktop, proiector, TV etc.).

Unul Digilent Zybo va fi conectat prin HDMI la dispozitivul de transmisie, iar celălalt va fi conectat prin HDMI la dispozitivul receptor.

Comunicația fără fir se va face utilizând o rețea locală fără fir dedicată emițătorului și receptorului, fără a fi direcționată printr-un router de acasă sau alt dispozitiv. Modulul wireless utilizat pentru acest proiect este tplink wr802n nanorouter, dintre care unul funcționează ca punct de acces pentru stabilirea rețelei și celălalt pentru a funcționa ca client pentru conectarea la rețea. Fiecare nanorouter va fi conectat prin cablu Ethernet la oricare dintre plăcile Zybo. Când sunt conectate la aceste routere, dispozitivele vor comunica prin TCP ca și cum ar fi fost conectate cu un singur cablu Ethernet (ceea ce înseamnă că singura configurație necesară pentru a stabili o conexiune este adresa IP a clientului).

În timp ce obiectivul proiectului a fost de a facilita un flux de 1080x720 video @ 60Hz, acest lucru nu a fost realizabil din cauza limitărilor lățimii de bandă din rețeaua wireless și a lipsei compresiei video în timp real pentru a reduce datele necesare pentru a trimite. În schimb, acest proiect servește drept cadru pentru dezvoltarea viitoare pentru a atinge acest obiectiv, deoarece a restricționat sever limitările ratei de cadre pentru a transmite în mod corespunzător date HDMI, așa cum se intenționează.

Cerințe de proiect:

2 plăci de dezvoltare Digilent Zybo (trebuie să aibă cel puțin un port HDMI)

2x cabluri HDMI

2x cabluri microusb (pentru a conecta Zybo la computer pentru dezvoltare)

2x nanoroutere tplink wr802n (inclusiv adaptoare 2x adaptoare de alimentare cu microb și priză de perete)

2x cabluri ethernet

*** Notă: Acest tutorial presupune familiaritatea cu suita de design Vivado și experiența de creare a unui nou proiect și design de blocuri. ***

Pasul 1: Configurați logica programabilă Zynq pentru emițător

Abordarea noastră de a dezvolta logica programabilă a transmițătorului a fost de a efectua o trecere hdmi-la-hdmi de la PC pentru a monitoriza folosind două blocuri Video Direct Memory Access (VDMA), unul pentru scriere și unul pentru citire.

Ambele sunt selectate pentru modul de funcționare liber, cu 3 cadre tampon (0-1-2). Deoarece nucleul video este optimizat pentru 60 de cadre pe secundă, aceasta înseamnă că VDMA va scrie sau citi într-un cadru nou la fiecare 16,67 ms în această ordine: 0, 1, 2, 0, 1, 2, 0, 1, 2. Locațiile de memorie DDR pentru fiecare cadru sunt diferite pentru cele două VDMA, deoarece nu mai sunt sincronizate între ele. În schimb, un temporizator hardware (TTC1), configurat pentru 60 Hz, este utilizat pentru a sincroniza mișcarea datelor între cele două locații de memorie.

Imaginea de mai sus prezintă 3 cadre, dimensiunile acestora și cantitatea de memorie necesară de fiecare (în dreapta cadrului). Dacă atribuim VDMA de scriere acestor locații de memorie, atunci putem atribui locațiile de memorie VDMA citite dincolo de acest set, să spunem începând cu 0x0B000000. Fiecare cadru este format din 1280 * 720 pixeli și fiecare pixel este format din 8 biți de roșu, verde și albastru pentru un total de 24 de biți. Aceasta înseamnă că un cadru este format din 1280 * 720 * 3 octeți (2,76 MB).

În interiorul temporizatorului IRQ, care este descris în configurarea driverului VDMA, se va ocupa de copierea datelor între cele două locații de memorie VMDA. VDMA oferă un pointer către cadrul curent în care se scrie sau se citește. Cadrul este reprezentat de un anumit cod gri, care este convertit în software. Definițiile codului gri pentru o configurație cu 3 cadre-tampon pot fi găsite în Ghidul produsului AXI VDMA din apendicele C.

Acest lucru ne permite să copiem conținutul scris în memorie fără a citi dintr-un cadru în care se scrie în prezent.

*** Rețineți că VDMA citit nu este utilizat atunci când trimiteți date prin rețeaua wireless. Singurul scop este să verifice funcționarea corectă a copierii memoriei din VMDA de scriere. Citirea VMDA ar trebui să fie dezactivată. ***

Iată pașii pentru crearea blocului de proiectare a emițătorului:

- Când creați un proiect nou, este o idee bună să atribuiți un cip sau o placă proiectului. Acest link descrie cum să adăugați fișiere de bord noi în directorul Vivado și să asociați placa corectă cu proiectul dumneavoastră. Va fi util la adăugarea blocului Sistem de procesare și la trecerea de la hardware la software (partea SDK).

-

Adăugați următoarele blocuri:

- dvi2rgb

- Intrare video în fluxul Axi4

- Controler de sincronizare

- axi4-stream pentru a ieși

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Vrăjitorul cu ceas

- Constant

- Sistem de procesare Zynq

- Când adăugați sistemul de procesare, faceți clic pe „Rulați automatizarea blocului” din bara superioară de culoare verde și asigurați-vă că este selectată opțiunea „Aplicare presetare placă”. Lăsați orice altceva implicit.

- Imaginile fiecărei ferestre de configurare a blocurilor pot fi găsite în imaginile de mai sus. Dacă nu vedeți o imagine pentru o anumită fereastră, lăsați-o ca implicită.

-

Începeți configurarea sistemului Zynq Processing:

- În configurația PS-PL AXI Non Secure Enable GP Master AXI, activați interfața M AXI GP0

- În configurația PS-PL HP Slave AXI Interface, activați atât HP0, cât și HP1

- În configurația MIO Asigurați-vă că ENET0 este activat în periferice I / O, apoi Unitate procesor aplicație, activați Timer0

- În Clock Configuration PL Fabric Clocks, activați FCLK_CLK0 și setați la 100 MHz.

- Faceți clic pe Ok

- Înainte de a da clic pe „Rulați automatizarea conexiunii”, asigurați-vă că conectați blocurile video așa cum se vede în imaginea de proiectare a blocului TX de mai sus. Veți dori să redenumiți constanta la VDD și să setați valoarea la 1. Conectați blocurile video în consecință.

- Faceți ceasul HDMI TMDS și pinii de date externi pe blocurile rgb2dvi și dvi2rgb

- Creați un port de intrare și ieșire pentru semnalul de detectare hot plug (HPD) și conectați-le împreună, acestea sunt definite în fișierul de constrângeri

-

Ceasul pixelilor este recuperat din TMDS_Clk_p, care este creat în fișierul de constrângeri. Acesta va fi de 74,25 MHz în conformitate cu rezoluția 720p. Este important să conectați ceasul pixelilor (de la blocul dvi2rgb) la următorii pini:

- vid_io_in_clk (vid în blocul fluxului axi)

- vid_io_out_clk (fluxul axi în blocul vid out)

- clk (controler de sincronizare)

- PixelClk (rgb2dvi)

- *** Notă: În prezent, pentru a activa recuperarea ceasului pixelilor, conectorii HDMI rx și tx trebuie conectați la o sursă / chiuvetă activă. O modalitate în acest sens este separarea blocurilor video rx și tx în diferite domenii de ceas (cu alte cuvinte, generați un nou ceas de 74,25 MHz pentru a alimenta blocul tx). ***

- Apoi configurați vrăjitorul de ceas, astfel încât să aveți o intrare de 100 MHz (sursă globală de tampon) și 3 ceasuri de ieșire la 50 MHz (ceas AXI-Lite), 150 MHz (ceas AXI4-Stream), 200 MHz (pin RefClk dvi2rgb).

- Conectați pinul sistemului de procesare FCLK_CLK0 la intrarea vrăjitorului de ceas

- În acest moment, faceți clic pe „Rulați automatizarea conexiunii” din bara verde din partea de sus a ferestrei de proiectare. Este o idee bună să faceți acest lucru pentru un bloc odată și să urmați imaginea de proiectare a blocului TX de mai sus.

- Instrumentul va încerca să adauge interconectarea AXI, care acționează ca interconectare master / slave pentru blocurile care utilizează magistrala AXI-Lite (VDMA și GPIO).

- De asemenea, va adăuga AXI SmartConnect, care acționează ca interconectare master / slave pentru interfețele de procesor AXI4-Stream și High Performance utilizate de VDMA (Stream to Memory Map și invers).

- Instrumentul va adăuga, de asemenea, o resetare a sistemului procesorului. Asigurați-vă că acest lucru este conectat doar la blocurile VDMA, GPIO și procesor. Nu-l conectați la niciun bloc video (de exemplu, dvi2rgb, controler de sincronizare, vid pentru flux etc.)

- Odată ce automatizarea conexiunii a fost finalizată, verificați dacă conexiunile se potrivesc cu imaginea de proiectare a blocului TX. Veți observa un bloc ILA suplimentar de sistem care nu a fost menționat. Aceasta este doar pentru depanare și nu este necesară pentru moment. Folosește resetarea procesorului de 150 de milioane, deci nici acest lucru nu este necesar. Oriunde vedeți mici „bug-uri” verzi pe autobuze, asta din cauza ILA și poate fi ignorat.

- Ultimul pas este să faceți clic dreapta pe designul blocului din arborele surselor proiectului și să selectați „Creați HDL Wrapper”. Dacă intenționați să adăugați logică la ambalaj, aceasta va fi suprascrisă de fiecare dată când este selectat.

- Consultați secțiunea Configurare driver VDMA pentru detalii din partea SDK.

Ceasuri și resetări

Am constatat că cele mai importante aspecte ale oricărui proiect logic programabil este luarea în considerare atentă a domeniilor de ceas și a semnalelor de resetare. Dacă acestea sunt configurate corespunzător, aveți o idee bună pentru a face ca designul dvs. să funcționeze.

Ceas Pixel și sincronizare blocată

Pentru a verifica dacă anumite semnale sunt active, este o idee bună să legați aceste semnale la LED-uri (ceasuri, resetări, blocări etc.). Două semnale pe care le-am găsit utile pentru a le urmări pe placa emițătorului au fost ceasul pixelilor și semnalul „blocat” de pe blocul de ieșire video AXI4-Stream, care vă spune că sincronizarea video a fost sincronizată cu controlerul de sincronizare și sursa video date. Am adăugat o oarecare logică învelișului de bloc de proiectare care urmărește ceasul pixelilor utilizând semnalul PixelClkLocked de pe blocul dvi2rgb ca resetare. Am atașat fișierul ca hdmi_wrapper.v aici. Fișierul de constrângeri este, de asemenea, atașat aici.

Pasul 2: Configurați logica programabilă Zynq pentru receptor

Blocul Logic programabil pentru receptor este mai simplu. Diferența cheie, alta decât blocurile de intrare hdmi lipsă, este absența unui ceas de pixeli recuperat. Din acest motiv, trebuie să ne generăm propriile noastre din vrăjitorul de ceas. Această proiectare trebuie realizată într-un proiect separat de transmițător. În scopurile noastre, proiectul receptorului a urmat placa Zybo 7Z-20, în timp ce Transmițătorul a urmat placa Z7-10. FPGA-urile de pe plăci sunt diferite, așa că … fii atent.

Iată pașii pentru crearea blocului de proiectare a receptorului:

-

Adăugați următoarele blocuri IP la design:

- Controler de sincronizare

- AXI4-Stream către ieșire video

- RGB la DVI

- AXI VDMA

- AXI GPIO

- Sistem de procesare

- Vrăjitorul cu ceas

- Constant (VDD setat la 1)

- Urmați același model pentru configurarea acestor blocuri ca și Transmițătorul. Au fost incluse aici imagini pentru diferențele notabile în configurație. Celelalte rămân la fel ca Transmițătorul.

- Configurați VDMA pentru acest design numai ca canal de citire. Dezactivați canalul de scriere.

-

Expertul pentru ceas trebuie configurat pentru următoarele ieșiri:

- clk_out1: 75 MHz (ceas pixel)

- clk_out2: 150 MHz (ceas de flux)

- clk_out3: 50 MHz (ceas axi-lite)

- Conectați blocurile video așa cum se arată în imaginea de proiectare a blocului RX.

- Apoi rulați automatizarea conexiunii, care va adăuga blocurile AXI Interconnect, AXI SmartConnect și System Reset și va încerca să efectueze conexiunile corespunzătoare. Mergeți încet aici pentru a vă asigura că nu realizează conexiuni nedorite.

- Faceți ceasul HDMI TMDS și pinii de date externi pe blocul rgb2dvi

- Nu este nevoie de semnal hot plug pe acest design.

Pasul 3: Configurați driverul VDMA

Configurarea pentru diferitele blocuri care sunt configurate prin interfața AXI-Lite se face cel mai bine utilizând proiecte demo incluse în BSP ca referință. După exportarea hardware-ului de proiectare și lansarea SDK-ului de la Vivado, veți dori să adăugați un nou pachet de suport pentru placă și să includeți biblioteca lwip202 în fereastra de setări BSP. Deschideți fișierul fișier system.mss din BSP și veți vedea driverele periferice prezente din designul blocului. Opțiunea „Importa exemple” vă permite să importați proiecte demo care utilizează aceste periferice și vă arată astfel cum să le configurați în software folosind driverele Xilinx disponibile (a se vedea imaginea atașată).

Aceasta a fost metoda utilizată pentru configurarea VDMA, Timer & Interrupt și GPIO. Codul sursă atât pentru transmis cât și pentru recepție a fost inclus aici. Diferențele sunt aproape exclusiv în main.c.

*** NOTĂ: Deoarece sistemul nu este complet funcțional în momentul redactării acestui tutorial, codul sursă din această secțiune nu include codul de rețea fără fir. Mai multe erori trebuie soluționate ca urmare a combinării proiectelor de transmisie / recepție de bază video cu proiecte de transmisie / recepție de rețea. Prin urmare, acest tutorial le tratează separat pentru moment. ***

Funcția de manipulare a întreruperii TX (IRQHandler)

Această funcție citește codurile gri furnizate de VDMA de citire și scriere prin intermediul blocurilor GPIO. Codurile gri sunt convertite în zecimale și utilizate pentru selectarea locației de memorie de bază a cadrului cadrului curent. Cadrul copiat este cadrul anterior la cel pe care este scris de VDMA (de exemplu, dacă VDMA scrie în cadrul 2, copiem cadrul 1; dacă scrie în cadrul 0, înfășurăm și citim din cadrul 2).

Funcția captează doar fiecare al șaselea cadru pentru a reduce rata cadrelor la 10 Hz mai degrabă decât la 60 Hz. Limita superioară a rețelei este de 300 Mbps. La 10 cadre pe secundă este necesară o lățime de bandă de 221,2 Mbps.

Comentarea / necomentarea a două linii în această funcție îi va permite utilizatorului să treacă la modul HDMI passthru în scopuri de depanare / testare (codul este comentat pentru a indica liniile corespunzătoare). În prezent, copiază cadrul într-o locație de memorie utilizată de codul Ethernet.

Funcția de manipulare a întreruperii RX (IRQHandler)

Această funcție este foarte asemănătoare cu funcția TX, dar copiază dintr-un FIFO cu 2 buffere utilizate de Ethernet pentru a scrie date primite. Codul ethernet indică în ce cadru se scrie în FIFO, datele sunt copiate din cadrul opus. Datele sunt copiate în cadrul direct din spatele celui citit de VDMA pentru a evita ruperea.

Pasul 4: Configurați rețeaua Nanorouter

Pentru a crea o rețea utilizând nanorouterele TPlink, porniți-le individual și conectați-vă la SSID-ul wifi implicit pentru dispozitive. Mai multe informații despre setările de configurare pentru acest dispozitiv pot fi găsite prin intermediul manualului de utilizare al dispozitivului.

Configurați unul dintre dispozitive ca punct de acces, acesta va acționa ca conexiune principală pentru rețea. Asigurați-vă că denumiți rețeaua și notați numele și dezactivați DHCP (nu vrem ca routerul să configureze adresele IP dinamic, dorim ca plăcile Zybo pentru emițător și destinatar să își seteze ele însele adresele IP, astfel încât acestea să fie consistente). După configurare, asigurați-vă că dispozitivul repornește și stabilește această rețea.

Configurați celălalt dispozitiv ca client și asigurați-vă că acesta se conectează la SSID-ul de rețea pe care l-ați configurat cu primul nanorouter. Încă o dată, asigurați-vă că DHCP este dezactivat pentru client.

Odată ce clientul a terminat și a repornit, acesta ar trebui să se conecteze la punctul de acces nanorouter (dacă nu, probabil că există o problemă în configurația dvs. pentru unul dintre dispozitive). Veți observa că lumina LED de pe client va fi solidă odată ce s-a conectat la punctul de acces.

LED-ul punct de acces nanorouter probabil va continua să clipească în acest moment, este în regulă! Lumina intermitentă înseamnă că nu este conectat la un alt dispozitiv din portul său Ethernet și, odată ce este conectat la un Zybo configurat, LED-ul va rămâne solid indicând o conexiune de rețea reușită.

Acum că avem configurarea nanorouterelor, avem o rețea fără fir care ne va permite să comunicăm prin. O notă importantă este că metoda noastră de configurare pentru nanoroutere (ca punct de acces și client) ne permite să comunicăm de pe placa Zybo de transmisie către placa Zybo de primire ca și cum cei doi ar fi conectați cu un singur fir Ethernet. Acest lucru face ca configurarea rețelei noastre să fie mai puțin dificilă, deoarece alternativa ar include probabil configurarea plăcilor Zybo pentru a se conecta în mod explicit la server împreună cu conexiunea intenționată.

Odată ce ambele dispozitive sunt configurate, nanorout-urile sunt configurate și gata să fie implementate în rețeaua WIDI. Nu există o asociere specifică între nanoroutere și plăcile Zybo, deoarece punctul de acces sau clientul vor funcționa fie pentru dispozitivul de transmisie, fie pentru cel de recepție.

Pasul 5: Configurați sistemul de procesare Zynq pentru transmiterea datelor prin Ethernet

Pentru a transmite datele HDMI de la o placă Zybo la cealaltă, trebuie să încorporăm un protocol Ethernet cu driverul nostru VDMA. Scopul nostru aici este de a transmite cadre video individuale prin perifericul Ethernet în sistemul de procesare, la o rată stabilită care este în concordanță cu lățimea de bandă a rețelei noastre. Pentru proiectul nostru, am folosit TCP furnizat de API-ul LwIP bare-metal. Întrucât ambii membri ai proiectului sunt relativ neexperimentați cu utilitățile de rețea, această alegere a fost făcută fără a recunoaște pe deplin implicațiile și constrângerile implicate în TCP. Problema majoră cu această implementare a fost lățimea de bandă limitată și faptul că nu este concepută cu adevărat în scopul obținerii unor volume mari de date. Soluțiile alternative pentru înlocuirea TCP și îmbunătățirea acestui proiect vor fi discutate mai târziu.

O scurtă descriere a TCP cu LwIP: Datele sunt trimise prin rețea în pachete de dimensiunea tcp_mss (dimensiunea maximă a segmentului TCP), care este în general de 1460 octeți. Apelarea tcp_write va lua unele date la care face referire un pointer și va configura pbufs (tampoane de pachete) pentru a păstra datele și a oferi o structură pentru operațiunile TCP. Cantitatea maximă de date care poate fi coadă la un moment dat este setată ca tcp_snd_buf (spațiu tampon expeditor TCP). Deoarece acest parametru este un număr de 16 biți, suntem limitați la o dimensiune a bufferului de trimitere de 59695 octeți (există unele umpluturi necesare în bufferul de trimitere). Odată ce datele au fost puse în coadă, tcp_output este chemat pentru a începe transmiterea datelor. Înainte de a trimite următorul segment de date, este imperativ ca toate pachetele anterioare să fi fost transmise cu succes. Acest proces se realizează utilizând funcția recv_callback, deoarece aceasta este funcția care este apelată atunci când confirmarea este văzută de la receptor.

Utilizarea exemplelor de proiecte în Vivado SDK este foarte utilă pentru a afla cum funcționează LwIP TCP și este un bun punct de plecare pentru începerea unui nou proiect.

Procedura pentru dispozitivul de transmisie WiDi este următoarea:

- Inițializați rețeaua TCP folosind apelurile de funcții ale driverului LWIP din metal.

- Specificați toate funcțiile de apelare necesare pentru operațiunile de rețea.

- Conectați-vă la receptorul WiDi conectându-vă la adresa și portul IP (configurația noastră: IP-ul receptorului este 192.168.0.9, conectați-vă la portul 7).

- Când expiră cronometrul driverului VDMA, introduceți TX ISR.

- Determinați bufferul cadru curent pentru acces pe baza codului gri VDMA

- Așezați primul segment de date în bufferul de trimitere TCP

- Trimiteți datele și actualizați variabilele locale pentru a urmări cât de multe date au fost trimise din cadrul curent.

- La atingerea apelului de apel primit (apel funcțional efectuat după ce emițătorul primește o confirmare de recuperare a datelor), puneți în coadă următorul segment de date.

- Repetați pașii 7 și 8 până când a fost trimis întregul cadru.

- Reveniți la o stare de repaus pentru a aștepta următoarea întrerupere a temporizatorului pentru a indica că este pregătit un nou cadru (înapoi la pasul 4).

Asigurați-vă că configurați setările LwIP pentru pachetul de asistență al plăcii, așa cum se arată în imaginea de mai sus. Toate valorile sunt implicite, cu excepția tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. De asemenea, rețineți că depanarea detaliată poate fi realizată prin modificarea parametrilor BSP pentru grupul debug_options.

Pasul 6: Configurați sistemul de procesare Zynq pentru recepția datelor prin Ethernet

Placa de dezvoltare Zybo care va acționa ca receptor wireless va funcționa similar cu dispozitivul de transmisie. Setările pachetului de asistență pentru LwIP vor fi identice cu cele din pasul anterior.

Dispozitivul va prelua pachete care conțin segmentele de cadre video de la nanorouter și va copia datele cadrului video în spațiul tampon cu trei cadre pentru VDMA de recepție. Pentru a evita suprascrierea oricăror date, se utilizează un tampon de date dublu (vom numi tamponul de rețea) la colectarea de date de la nanorouter, astfel încât traficul de rețea să poată continua fluxul în timp ce cadrul video complet anterior este copiat în Tampon VDMA.

Procedura pentru dispozitivul de recepție WiDi necesită două activități, dintre care una este primirea de date Ethernet, iar cealaltă este copierea cadrelor video din bufferul de rețea în bufferul triplu frame al VDMA.

Sarcină de recepție Ethernet:

- Inițializați rețeaua TCP folosind apelurile funcționale ale driverului LWIP din metal (configurare cu adresa IP la care se va conecta emițătorul, 192.168.0.9 în a noastră)

- Specificați toate funcțiile de apelare necesare pentru operațiunile de rețea.

- După primirea pachetului ethernet, copiați datele pachetului în bufferul de rețea curent, creșteți datele acumulate curente.

- Dacă pachetul umple tamponul cadrului de rețea, continuați cu pașii 5 și 6. În caz contrar, reveniți la pasul 3 din această sarcină.

- semnalează faptul că sarcina tampon VDMA triplă cadru ar trebui să copieze din tamponul de rețea nou finalizat.

- Treceți la celălalt buffer de rețea și continuați să colectați date prin Ethernet.

- Repaus până când se primește un nou pachet ethernet (pasul 3).

Copiați bufferul de rețea în bufferul VDMA cu trei cadre:

- Când expiră cronometrul driverului VDMA, introduceți RX ISR.

- Determinați bufferul cadru curent pentru acces pe baza codului gri VDMA.

- Determinați care tampon de rețea va fi copiat în bufferul VDMA și copiați aceste date

Pasul 7: Conectați-vă plăcile Zybo la sursa HDMI și la chiuveta HDMI

Acum conectați cablurile HDMI atât pentru receptor cât și pentru transmițător, programați FPGA și rulați sistemul de procesare. Frecvența de cadre va fi probabil foarte lentă, datorită cheltuielilor imense în operațiunea LwIP și a lățimii de bandă limitate. Dacă există probleme, conectați-vă prin UART și încercați să identificați orice avertismente sau erori.

Pasul 8: Idei alternative pentru îmbunătățire

O mare problemă pentru acest proiect a fost cantitatea de date necesare pentru a trimite prin Wi-Fi. Acest lucru era de așteptat, cu toate acestea, am subestimat impactul pe care acesta l-ar avea și a avut ca rezultat mai mult o explozie de imagini pe un ecran, mai degrabă decât un flux video. Există mai multe modalități de a îmbunătăți acest proiect:

- Compresie video în timp real. Comprimarea fluxului video de intrare cadru cu cadru ar reduce considerabil cantitatea de date care trebuie trimise prin rețea. În mod ideal, acest lucru s-ar face în hardware (ceea ce nu este o sarcină ușoară) sau s-ar putea face în software utilizând celălalt nucleu ARM pentru a rula algoritmi de compresie (acest lucru ar necesita o analiză suplimentară pentru a se asigura că timpul funcționează). Există câteva componente open source de compresie video în timp real pe care le-am găsit pe web, dar majoritatea sunt IP.

- Implementarea fluxului Ethernet în hardware, mai degrabă decât în software. A existat o tonă de cheltuieli generale din cauza lipsei de spațiu disponibil pentru coada datelor de ieșire în transmițător, din cauza limitării dimensiunii segmentului. Un proces mult mai eficient este utilizarea IP-ului AXI Ethernet cu un buffer FIFO sau DMA pentru a introduce date în acesta. Acest lucru ar reduce bagajul suplimentar de la LwIP TCP și ar permite un flux mai mare de date.

Pasul 9: Accesibilitate

Produsul rezultat al acestui proiect WiDi ar trebui să fie o pereche de dispozitive compacte complet integrate, pe care un utilizator să le poată conecta la orice sursă HDMI și apoi să scadă alimentarea video pe un afișaj cu capacitate HDMI fără fir. Dispozitivele vor avea SoC Zynq-7000 găsit pe placa de referință Zybo și vor încorpora hardware-ul de rețea găsit în nano-routerele TP-Link. În mod ideal, utilizatorul ar putea controla modulul de transmisie dintr-o locație discretă din cadrul sistemului de operare țintă, cu puțină nevoie de abilități tehnice semnificative.

Securitate și conectivitate

Dispozitivele ar trebui să includă, de asemenea, Transport Layer Security (TLS) și să aibă capacitate limitată de conectare automată, atât în scopuri de confidențialitate. Este intenția proiectanților de a face conexiunea cu un afișaj prin intermediul unei interfețe wireless o acțiune deliberată în numele utilizatorului pentru a evita difuzarea greșită a materialelor sensibile.

Stare actuală

Până în acest moment, starea proiectului este încă o lucrare în curs. Pentru ca utilizatorul actual al punctului final să beneficieze de acest tutorial, el sau ea trebuie să aibă o înțelegere tehnică puternică a proiectării sistemului încorporat și ar trebui să aibă o anumită familiaritate cu hardware-ul programabil și software-ul încorporat care lucrează împreună.

Datele trimise prin rețea nu sunt criptate în acest moment și se presupune că este o transmisie brută a pachetelor TCP / IP.

Proiectul video core a fost testat cu succes atât pentru transmisie, cât și pentru recepție. Pe de altă parte, conexiunea fără fir între două plăci zybo a fost stabilită și datele cadrului de testare au fost trimise cu succes. Cu toate acestea, este încă necesar să combinați codul de rețea la fiecare proiect de bază video și să testați transmisia cadrelor video reale.

Recomandat:

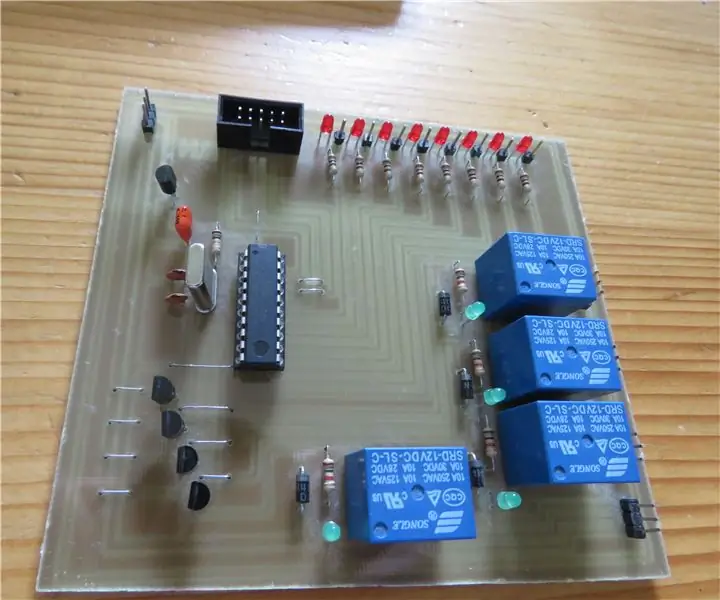

Placă de dezvoltare DIY ESP32 - ESPer: 5 pași (cu imagini)

DIY ESP32 Development Board - ESPer: Deci, recent citisem despre o mulțime de IoT-uri (Internet of Things) și ai încredere în mine, abia așteptam să testez unul dintre aceste dispozitive minunate, cu capacitatea de a mă conecta la internet, eu însumi și pun mâna pe muncă. Din fericire, ocazia

Creați-vă propria placă de dezvoltare cu microcontroler: 3 pași (cu imagini)

Creați-vă propria placă de dezvoltare cu microcontroler: ați dorit vreodată să vă creați propria placă de dezvoltare cu microcontroler și nu știați cum. În acest instructiv vă voi arăta cum să o faceți. și programare. Dacă aveți vreo căutare

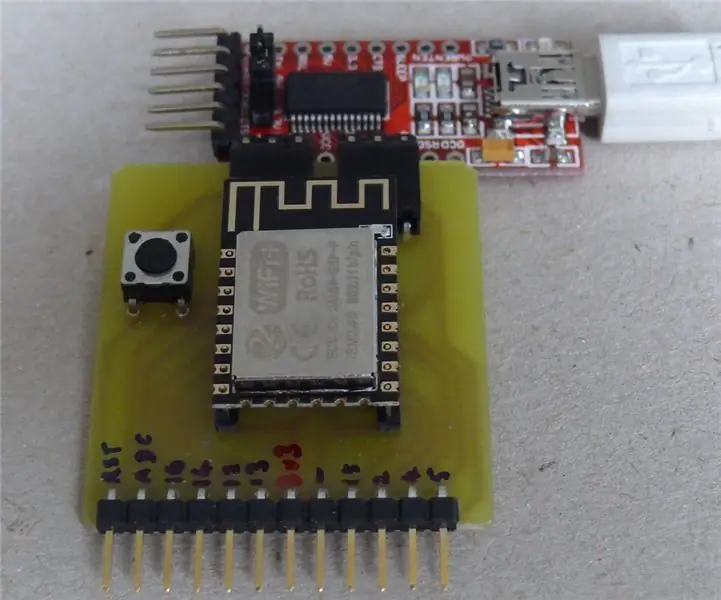

Placă de programare și dezvoltare ESP-12E și ESP-12F: 3 pași (cu imagini)

Placă de programare și dezvoltare ESP-12E și ESP-12F: Misiunea pentru această placă a fost simplă: să puteți programa modulele ESP-12E și ESP-12F la fel de ușor ca plăcile NodeMCU (adică nu este nevoie să apăsați butoanele). Aveți știfturi prietenoase cu panoul de acces cu acces la IO utilizabil. Utilizați un USB separat pentru a transmite serial

Quadcopter folosind placa Zybo Zynq-7000: 5 pași

Quadcopter folosind placa Zybo Zynq-7000: Înainte de a începe, iată câteva lucruri pe care le doriți pentru proiect: Lista pieselor 1x placa Digilent Zybo Zynq-7000 1x Cadru Quadcopter capabil să monteze Zybo (fișier Adobe Illustrator pentru tăiere cu laser atașat) 4x Turnigy D3530 / 14 Motoare fără perii 1100KV 4x

Domnul E.Z. Placă de dezvoltare a tubului: 4 pași (cu imagini)

Domnul E.Z. Consiliul de dezvoltare a tuburilor: Scop / scop: Domnul E.Z. Tube este o platformă audio ieftină pentru tuburi de vid fără „fier”: fără transformator de putere, fără transformatoare de ieșire. Un amplificator cu tub va avea de obicei mai multe transformatoare grele, scumpe: transformatoare de ieșire care protejează vorbitorul