Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:43.

- Modificat ultima dată 2025-01-23 15:04.

Conectați placa de dezvoltare Mojo la intrările externe cu acest scut.

Ce este placa de dezvoltare Mojo?

Placa de dezvoltare Mojo este o placă de dezvoltare bazată pe Xilinx spartan 3 FPGA. Tabloul este realizat de Alchitry. FPGA sunt foarte utile în cazul în care mai multe procese trebuie executate simultan.

De ce vei avea nevoie?

Provizii

Consiliul de dezvoltare Mojo

Fișier Gerber

8 x rezistențe de 15k ohm (opțional *)

Rezistențe de 4 x 470 ohmi

Rezistențe de 4 x 560 ohmi

4 x afișaje CC cu șapte segmente

4 x LED-uri de 3 mm

4 x comutatoare tactile SPDT

Comutator DIP cu montare pe suprafață 1 x 4 poziții

2 x 25 pe 2 sau 4 x 25 anteturi

1x cap de cutie 2 x 5 pini

Ciocan de lipit

Solder

Flux

* (în cazul în care aceste rezistențe sunt omise, pullup-ul intern / derulantul trebuie activat pentru pinii relevanți)

Pasul 1: Încărcați Gerber la producătorul Pcb la alegere

Pentru panourile mele am comandat de la JLC PCB.

Singura schimbare pe care am făcut-o a fost culoarea pe care am vrut să o potrivesc cu negrul Mojo.

Pasul 2: Adunarea consiliului

Când lipiți, întotdeauna mi se pare util să lipiți mai întâi cele mai mici părți, așa că începeți cu rezistențele este o idee bună.

R5, R6, R7, R8, R9, R10, R11 și R12 sunt rezistențe de 15k ohm folosite pentru a trage în jos comutatoarele (dacă utilizați pullup / pulldown intern ignorați acest lucru).

R1, R2, R3, R4 sunt rezistențe de 560 ohmi care sunt responsabile pentru limitarea curentului prin afișajul pe 7 segmente.

R13, R14, R15, R16 sunt rezistențe de 470 ohm care sunt responsabile pentru limitarea curentului prin cele 4 LED-uri.

Apoi lipiți comutatorul dip, comutatoarele tactile, LED-urile, afișajele cu șapte segmente și conectorul antetului cutiei în această ordine.

Acum puneți 25 cu 2 (sau 2 25 cu 1) în mojo pentru a alinia știfturile. Aliniați scutul cu știfturile și lipiți-l în poziție.

Pasul 3: Configurare software

Pentru software-ul care face trimitere la site-ul Alchitry vă va informa ce aveți nevoie pentru a începe și a instala Xilinx ISE. Cu toate acestea, schimbarea fișierului.ucf astfel încât să știe ce pini sunt conectați la ceea ce este important pentru a rula programul.

Iată fișierul.ucf pe care îl folosesc cu scutul:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODA "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Amintiți-vă dacă nu ați instalat rezistențele derulante pentru a edita pinii din.ucf cu

| TRAGE ÎN JOS; o

| TRAGE;

Dacă doriți să utilizați blocul pentru orice, conexiunile sunt după cum urmează. Stânga fiind numărul pinului de bloc și dreapta fiind numărul pinului mojo pe care ar trebui să-l atribuiți în.ucf:

pinul 1 = 29

pinul 2 = 51

pinul 3 = 32

pinul 4 = 41

pinul 5 = 34

pinul 6 = 35

pinul 7 = 40

pinul 8 = 33

pinul 9 = GND

pinul 10 = + V

Recomandat:

Configurare ST Visual Development Cu compilatorul Cosmic STM8: 11 pași

Configurarea dezvoltării vizuale ST cu compilatorul Cosmic STM8: Acesta este modul în care configurez mediul de dezvoltare integrat (IDE) pentru a programa microcontrolerele STM8 de la ST Microelectronics (ST) cu Windows 10. Nu susțin că acesta este modul corect, dar funcționează bine pentru mine. În acest instructabil va arăta ca un

FPGA Cyclone IV DueProLogic Controls Camera Raspberry Pi: 5 pași

FPGA Cyclone IV DueProLogic Controls Camera Raspberry Pi: În ciuda faptului că FPGA DueProLogic este conceput oficial pentru Arduino, vom face FPGA și Raspberry Pi 4B comunicabile. Trei sarcini sunt implementate în acest tutorial: (A) Apăsați simultan cele două butoane pe FPGA pentru a răsturna unghiul de

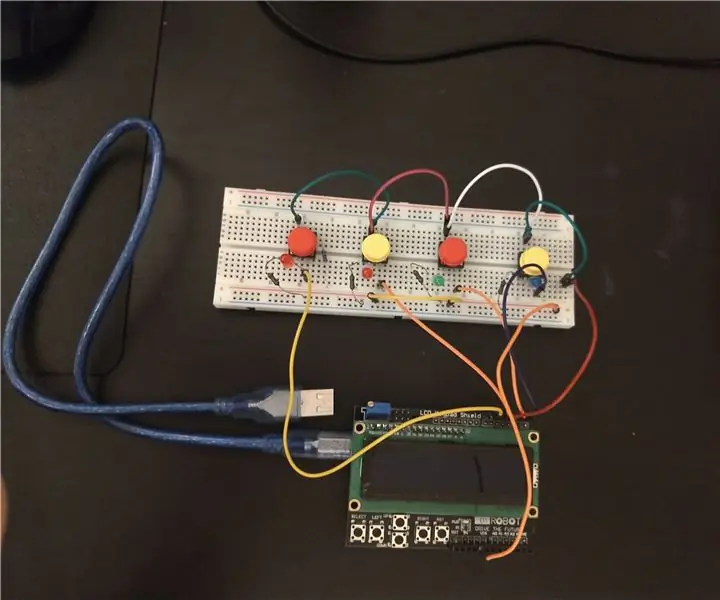

Led Reactie Spel Met Shield Keypad Shield: 4 pași

Led Reactie Spel Met Lcd Keypad Shield: Vrei să spui cum să faci școala cu arduino? Klinkt leuk! Dan moet je eerst een idee hebben voor een spel. Ik dacht meteen aan spellen waar je snel op een knop moet drukken als hij licht geeft. Dus ik keek op het internet in vond een project

JALPIC One Development Board: 5 pași (cu imagini)

JALPIC One Development Board: Dacă urmați proiectele mele Instructables știți că sunt un mare fan al limbajului de programare JAL în combinație cu microcontrolerul PIC. JAL este un limbaj de programare Pascal dezvoltat pentru microcontrolerele PIC pe 8 biți ale Microchip. Mo

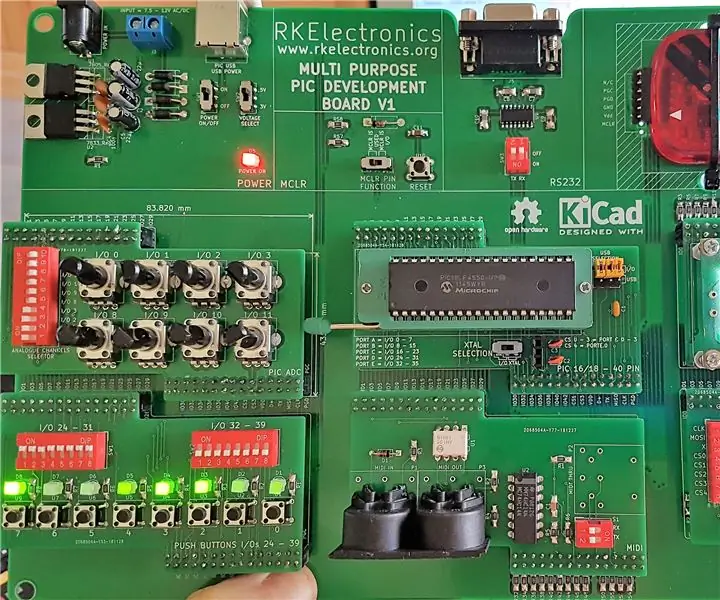

PIC Microcontroller Development Board System: 3 pași

PIC Microcontroller Development Board System: Acest proiect este destinat proiectării și utilizării unui instrument de dezvoltare PIC care este flexibil pentru a se potrivi unei game largi de proiecte electronice bazate pe PIC. care permit utilizatorilor