Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:41.

- Modificat ultima dată 2025-01-23 15:04.

De AmCoderhttps://www.linkedin.com/in/mitu Urmăriți mai multe de la autor:

Despre: Mitu Raj - Doar un hobbyst și un student - Chip Designer - Dezvoltator de software - Entuziast în fizică și matematică Mai multe despre AmCoder »

## Acesta este cel mai clicat link din Google pentru implementarea VHDL a CORDIC ALGORITHM pentru a genera undă sinusoidală și cosinus ## În prezent există mulți algoritmi eficienți hardware, dar aceștia nu sunt bine cunoscuți din cauza dominanței sistemelor software asupra mulți ani. CORDIC este un astfel de algoritm care nu este altceva decât un set de schimbare și adăugare de logici utilizate pentru calcularea unei game largi de funcții, inclusiv anumite funcții trigonometrice, hiperbolice, liniare și logaritmice. Acesta este algoritmul utilizat în calculatoare etc. Astfel, prin simpla utilizare a schimbătorilor și a adderilor simpli, putem proiecta un hardware cu o complexitate mai mică, dar puterea DSP utilizând algoritmul cordic. Prin urmare, poate fi proiectat ca un design RTL gol în VHDL sau Verilog fără a utiliza unități dedicate în virgulă mobilă sau IP-uri matematice complexe.

Pasul 1: VHDL și Modelsim

Aici algoritmul cordic este implementat folosind VHDL pentru a genera o undă sinusoidală și o undă cose. Poate emite sinus și cosinusul unghiului de intrare cu mare precizie. Codul este sintetizabil pe FPGA. Modelsim este utilizat pentru a simula proiectarea și banca de testare.

Pasul 2: Cod VHDL pentru proiectare și bancul de testare

Tehnica scalării binare este utilizată pentru a reprezenta numerele în virgulă mobilă.

Vă rugăm să treceți prin documentele atașate înainte de a codifica.

Treceți prin simularea cordic_v4.vhd - Designul - Intrarea este unghiulară în 32 de biți + bit de semn; poate procesa orice unghi de la 0 la +/- 360 grade cu o precizie de intrare de 0,000000000233 grade. Când dați intrare -> MSB este bitul de semn, iar restul de 32 de biți reprezintă magnitudine. cu precizie 0,00001526. Vă rugăm să rețineți că ieșirea este afișată în forma de compliment 2, dacă valoarea sinus sau cos respectivă este negativă. Simularea testb.vhd - Banc de testare pentru proiectare (1) Unghiuri de intrare și resetare de tragere = '0'. După doi pași de simulare, trageți resetarea la „1” și „rulați totul”. (2) În fereastra de simulare setați radioul semnalelor sin și cos ca zecimal și format> Analog (automat). (3) Micșorați pentru a vedea forma de undă corect.

Pasul 3: Fișiere atașate

(1) cordic_v4.vhd - Proiectare. (2) testb.vhd - Banc de testare pentru proiectare.

(3) Documentați cum să forțați intrările unghiulare și să convertiți rezultatele binare.

Actualizare: ACESTE FIȘIERE SUNT OBSELETE ȘI NU MAI SUNT FURNIZATE. Vă rugăm să utilizați fișiere din pasul următor

Pasul 4: Core IP Mini-Cordic - 16 biți

Limitarea implementării de mai sus este - frecvența de funcționare a ceasului mai lentă, mai scăzută din cauza efectuării calculelor într-un singur ciclu de ceas. Core IP Mini-Cordic - 16 biți

- Trasee critice distribuite pe mai multe cicluri pentru a îmbunătăți performanța. precedent. Banc de testare:

complet automatizat de la 0 la 360 de grade intrări unghiulare

Fișiere atașate: 1) mini cordic fișier principal vhdl2) mini banc de testare cordic3) Mini Cordic IP Core manual 4) Doc despre cum să forțați unghiurile și să convertiți rezultatele

Pentru orice întrebări, nu ezitați să mă contactați:

Mitu Raj

urmează-mă:

mail: iammituraj@gmail.com

### Descărcări totale: 325 până la 01.05.2021 ###

### Ultima modificare a codului: 07 iulie 2020 ###

Recomandat:

Inteligență artificială de joc de masă: algoritmul Minimax: 8 pași

Inteligența artificială a jocului de masă: algoritmul Minimax: V-ați întrebat vreodată cum sunt fabricate computerele împotriva cărora jucați în șah sau în dame? Ei bine, nu căutați mai departe de acest instructabil, deoarece vă va arăta cum să creați o inteligență artificială (AI) simplă, dar eficientă, utilizând algoritmul Minimax! Prin utilizarea

Cronometru de bază folosind placa VHDL și Basys3: 9 pași

Cronometru de bază folosind placa VHDL și Basys3: Bine ați venit la instrucțiunile despre cum să construiți un cronometru folosind placa de bază VHDL și Basys 3. Suntem încântați să vă împărtășim proiectul nostru! Acesta a fost un proiect final pentru cursul CPE 133 (Digital Design) la Cal Poly, SLO în toamna anului 2016. Proiectul pe care îl construim

Robot de auto-echilibrare folosind algoritmul PID (STM MC): 9 pași

Robot de autoechilibrare folosind algoritmul PID (STM MC): Recent s-a făcut multă muncă în echilibrarea de sine a obiectelor. Conceptul de auto-echilibrare a început cu echilibrarea pendulului inversat. Acest concept s-a extins și la proiectarea de aeronave. În acest proiect, am proiectat un mic mod

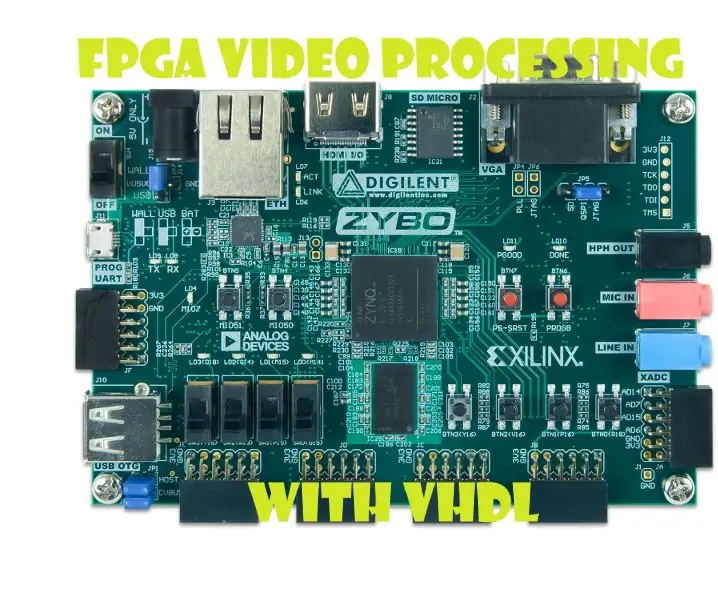

Procesare video folosind VHDL și un Zybo: 10 pași

Procesare video folosind VHDL și un Zybo: FPGA-urile sunt mai rapide de procesat decât CPU-urile, deoarece pot face multe calcule în paralel Notă: Acest proiect este încă în construcție și urmează să fie îmbunătățit (imediat ce am timp). Între timp călătoresc prin lume

Controlul vitezei motorului DC folosind algoritmul PID (STM32F4): 8 pași (cu imagini)

Controlul vitezei motorului de curent continuu folosind algoritmul PID (STM32F4): salut tuturor, asta este tahir ul haq cu un alt proiect. De data aceasta este STM32F407 ca MC. Acesta este un proiect de sfârșit de semestru. Sper că vă place. Necesită o mulțime de concepte și teorie, așa că mergem mai întâi în ea. Odată cu apariția computerelor și a