Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:43.

- Modificat ultima dată 2025-01-23 15:04.

Sunt copleșit de felul de răspunsuri pe care le primesc în acest blog. Mulțumesc băieți că mi-ați vizitat blogul și m-ați motivat să vă împărtășesc cunoștințele. De data aceasta, voi prezenta designul unui alt modul interesant pe care îl vedem în toate SOC-urile - Controler de întrerupere.

Vom proiecta un controler de întrerupere programabil simplu, dar puternic. Este un design complet configurabil și parametrizat, care este portabil pe platforme. Am proiectat acest lucru după ce am citit multe despre unele arhitecturi populare ale controlerelor de întrerupere, cum ar fi NVIC, 8259a, RISC-V PLIC, Microblaze's INTC, etc. cu ajutorul unui controler de întrerupere.

Pasul 1: Specificații

Următoarele sunt specificațiile IP:

- Interfață AHB3-Lite.

-

Parametri configurabili static:

- Nr. Surse de întrerupere externe; acceptă până la 63 de întreruperi.

- Nr. De niveluri de prioritate; suportă până la 63 de niveluri.

- Nr. Niveluri de cuibărit; suportă până la 8 niveluri de cuibărit.

- Latimea autobuzului; 32 sau 64.

- Întreruperi mascabile la nivel global și local.

- Nivel de prioritate configurabil dinamic pentru fiecare întrerupere.

- Două moduri de funcționare - modul complet imbricat și modul prioritate egală.

- Suportă întreruperi sensibile la nivel înalt activ.

Specificațiile RISC-V PLIC sunt folosite în proiect mecanismul de strângere a mâinii de întrerupere inspirat.

Preempțiunea de întrerupere este inspirată din 8259a

Altele citesc: Microblaze INTC, NVIC

Pasul 2: Prezentare generală a PIC

Controlerul de întrerupere programabil (PIC) primește mai multe întreruperi de la periferice externe și le îmbină într-o singură ieșire de întrerupere la un nucleu procesor țintă.

PIC este controlat prin registre de stare și control. Toate registrele PIC sunt mapate de memorie și accesate prin interfața magistralei AHB3-Lite.

Banca de registre este formată din registru de configurare, registre de activare, registre în așteptare, registre în serviciu, registre de priorități și registru de identificare, care sunt tipice în controlerele de întrerupere.

Registrul de configurare este utilizat pentru a seta modul de funcționare al PIC. Poate funcționa fie în modul complet imbricat, fie în modul cu prioritate egală.

Fiecărei întreruperi li se pot atribui priorități și pot fi mascate individual. Mascarea globală a tuturor întreruperilor este, de asemenea, acceptată.

Banca de registru interacționează cu Priority Resolver și BTC (Binary-Tree-Comparator) pentru a rezolva prioritățile întreruperilor în așteptare și pentru a afirma întreruperea procesorului în consecință. Registrul ID conține ID-ul celei mai mari priorități în așteptare.

Pasul 3: Proiectare și implementare RTL

Proiectul PIC accentuează reducerea latenței rezolvării priorităților, care este cea mai importantă parte a timpului în proiectare. Deoarece proiectarea rezolvă prioritățile într-un singur ciclu de ceas, performanța se degradează odată cu creșterea numărului de surse cu o complexitate Log2.

Proiectarea a fost implementată cu succes și sincronizarea a fost verificată până la următoarele frecvențe pe FPGA Artix-7.

- Până la 15 surse: 100 MHz

- Până la 63 de surse: 50 MHz

Latența de întrerupere adăugată doar de PIC este de 3 cicluri de ceas (Cu excepția timpului de comutare a contextului procesorului și a primului timp de preluare a instrucțiunilor ISR).

Pasul 4: Note importante și fișiere atașate

Notite importante:

- Dacă interfața AHB3-Lite nu este dorită, puteți schimba modulul superior și puteți utiliza scheletul PIC. Cu toate acestea, banca de testare furnizată este pentru IP cu interfață AHB3-Lite.

- PIC IP v1.0 este un design RTL complet portabil.

- Verificat funcțional pentru a funcționa în ambele moduri.

Fișiere atașate:

- Coduri de proiectare și testbench în VHDL.

- Documentație IP completă.

Este un design open-source … Simțiți-vă liber să folosiți …

Pentru orice întrebări, oricând:

Mitu Raj

Recomandat:

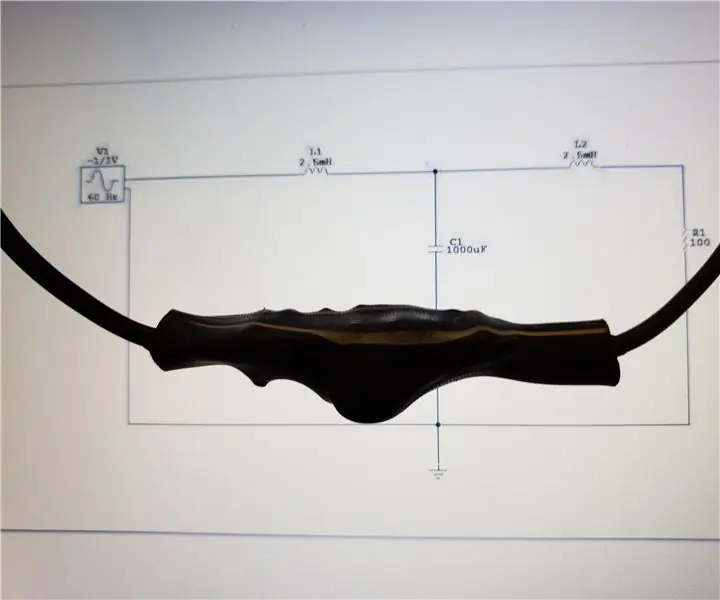

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: 5 pași

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: În acest manual, vă voi arăta cum să luați un cablu USB standard la mini USB, separați-l în mijloc și introduceți un circuit de filtrare care va reduce zgomotul excesiv sau hash produs de o sursă de alimentare tipică pentru Android. Am un portabil m

Proiectarea unui PCB de expansiune (Intel® IoT): 20 de pași

Proiectarea unui PCB de expansiune (Intel® IoT): acest instructabil a fost scris ca punct de plecare pentru cei care sunt dornici să utilizeze Intel® Edison la maximul său potențial, prin încorporarea acestuia într-un proiect încorporat complet dezvoltat. Pentru a face acest lucru, va trebui probabil să faceți - așa cum apelează Intel®

Proiectarea unui controler asociat asociat de cache simplu în patru direcții în VHDL: 4 pași

Proiectarea unui controler de cache asociativ setat în patru direcții în VHDL: În instructajul meu anterior, am văzut cum să proiectăm un controler de cache direct mapat simplu. De data aceasta, facem un pas înainte. Vom proiecta un controler cache asociativ simplu cu patru căi. Avantaj? Mai puțină rata de rate, dar cu prețul perfo

Proiectarea unui controller de cache simplu în VHDL: 4 pași

Proiectarea unui controler de cache simplu în VHDL: scriu acest lucru instructiv, pentru că mi s-a părut puțin dificil să obțin un cod VHDL de referință pentru a învăța și a începe proiectarea unui controler de cache. Așa că am proiectat un controler cache de la zero și l-am testat cu succes pe FPGA. Am p

Proiectarea unui controler VGA simplu în VHDL și Verilog: 5 pași

Proiectarea unui controler VGA simplu în VHDL și Verilog: În acest instructable, vom proiecta un controler VGA simplu în RTL. VGA Controller este circuitul digital conceput pentru a conduce afișaje VGA. Se citește din Frame Buffer (memorie VGA) care reprezintă cadrul care trebuie afișat și generează nece