Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:43.

- Modificat ultima dată 2025-01-23 15:04.

Scriu acest lucru instructiv, deoarece mi s-a părut puțin dificil să obțin un cod VHDL de referință pentru a învăța și a începe să proiectez un controler cache. Așa că am conceput un controler cache de la zero și l-am testat cu succes pe FPGA. Am prezentat aici un controler de cache direct mapat simplu, precum și am modelat un întreg procesor-sistem de memorie pentru a testa controlerul de cache. Sper că veți găsi acest lucru util ca o referință pentru a vă proiecta propriile controlere cache.

Pasul 1: Specificații

Acestea sunt principalele specificații ale controlerului de cache pe care urmează să îl proiectăm:

- Cartografiat direct. (accesați acest link dacă căutați un controler cache cache asociat)

- Memorie cache unică, blocată.

- Politica de scriere prin accesări la scriere.

- Politica de alocare fără scriere sau Scriere în jurul valorii de scriere.

- Fără tampon de scriere sau alte optimizări.

- Tag Array este încorporat.

În plus, vom proiecta și o memorie cache și un sistem de memorie principal.

Specificațiile implicite (configurabile) ale memoriei cache:

- Cache cu o singură bancă de 256 de octeți.

- 16 linii de cache, fiecare linie de cache (bloc) = 16 octeți.

Specificațiile memoriei principale:

- Memorie sincronă de citire / scriere.

- Memorie intercalată multi-bancară - patru bănci de memorie.

- Fiecare dimensiune a băncii = 1 kB fiecare. Prin urmare, dimensiunea totală = 4 kB.

- Memorie adresabilă Word (4 octeți) cu magistrală de adrese de 10 biți.

- Lățime de bandă mai mare pentru citire. Citiți lățimea datelor = 16 octeți într-un ciclu de ceas.

- Scrieți lățimea datelor = 4 octeți.

NOTĂ: verificați noul meu instructabil dacă sunteți în căutarea unui design asociativ al controlerului cache în 4 direcții

Pasul 2: Vizualizare RTL a întregului sistem

Reprezentarea completă RTL a modulului superior este prezentată în figură (cu excepția procesorului). Specificațiile implicite pentru autobuze sunt:

- Toate magistralele de date sunt magistrale pe 32 de biți.

- Address Bus = 32-bit Bus (Dar doar 10 biți sunt adresabili aici de memorie).

- Bloc de date = 128 biți (magistrală cu lățime de bandă largă pentru citire).

- Toate componentele sunt acționate de același ceas.

Pasul 3: Mediul de testare

Modulul de sus a fost testat folosind un banc de testare, care modelează pur și simplu un procesor fără conductă (deoarece proiectarea unui întreg procesor nu este deloc ușor !!). Test Bank generează frecvent cereri de citire / scriere în memorie. Acest lucru bate în joc instrucțiunile tipice „Încărcare” și „Stocare”, obișnuite în toate programele executate de un procesor. Rezultatele testului au verificat cu succes funcționalitatea controlerului cache. Următoarele sunt statisticile de testare observate:

- Toate semnalele de citire / scriere Miss și Hit au fost generate corect.

- Toate operațiile de citire / scriere a datelor au avut succes.

- Nu s-au detectat probleme de incoerență / inconsecvență a datelor.

- Proiectarea a fost verificată cu succes pentru un Maxm. Frecvența de funcționare a ceasului = 110 MHz în placa Xilinx Virtex-4 ML-403 (întreg sistem), 195 MHz numai pentru Cache Controller.

- Au fost deduse blocuri RAM pentru memoria principală. Toate celelalte matrice au fost implementate pe LUT-uri.

Pasul 4: Fișiere atașate

Următoarele fișiere sunt atașate aici cu acest blog:

- Fișiere. VHD ale Cache Controller, Cache Data Array, Main Memory System.

- Test Bank.

- Documentație despre controlerul cache.

Note:

- Consultați documentația pentru înțelegerea completă a specificațiilor controlerului cache prezentate aici.

- Orice modificare a codului depinde de alte module. Deci, schimbările ar trebui făcute judicios. Acordați atenție tuturor comentariilor și antetelor pe care le-am dat.

- Dacă, din orice motiv, blocurile RAM nu sunt deduse pentru memoria principală, REDUȚI dimensiunea memoriei, urmată de modificări ale lățimilor magistralei de adresă din fișiere și așa mai departe. Astfel, aceeași memorie poate fi implementată fie pe LUT-uri, fie pe RAM distribuită. Acest lucru va economisi timpul și resursele de rutare. Sau accesați documentația specifică FPGA și găsiți codul compatibil pentru Block RAM și editați codul în consecință și utilizați aceleași specificații ale lățimii magistralei de adrese. Aceeași tehnică pentru Altera FPGA.

Recomandat:

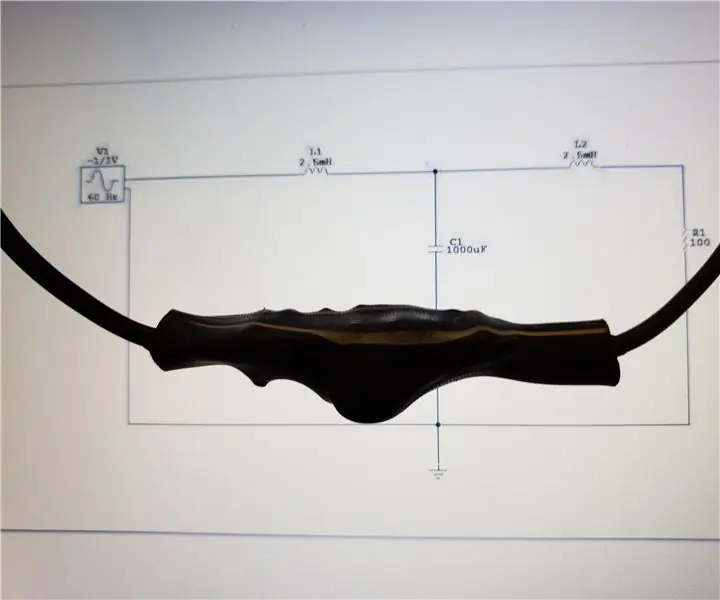

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: 5 pași

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: În acest manual, vă voi arăta cum să luați un cablu USB standard la mini USB, separați-l în mijloc și introduceți un circuit de filtrare care va reduce zgomotul excesiv sau hash produs de o sursă de alimentare tipică pentru Android. Am un portabil m

Proiectarea unui PCB de expansiune (Intel® IoT): 20 de pași

Proiectarea unui PCB de expansiune (Intel® IoT): acest instructabil a fost scris ca punct de plecare pentru cei care sunt dornici să utilizeze Intel® Edison la maximul său potențial, prin încorporarea acestuia într-un proiect încorporat complet dezvoltat. Pentru a face acest lucru, va trebui probabil să faceți - așa cum apelează Intel®

Proiectarea unui controler asociat asociat de cache simplu în patru direcții în VHDL: 4 pași

Proiectarea unui controler de cache asociativ setat în patru direcții în VHDL: În instructajul meu anterior, am văzut cum să proiectăm un controler de cache direct mapat simplu. De data aceasta, facem un pas înainte. Vom proiecta un controler cache asociativ simplu cu patru căi. Avantaj? Mai puțină rata de rate, dar cu prețul perfo

Proiectarea unui controler de întrerupere programabil în VHDL: 4 pași

Proiectarea unui controler de întrerupere programabil în VHDL: sunt copleșit de tipul de răspunsuri pe care le primesc în acest blog. Mulțumesc băieți că mi-ați vizitat blogul și m-ați motivat să vă împărtășesc cunoștințele. De data aceasta, voi prezenta designul unui alt modul interesant pe care îl vedem în toate SOC - Interrupt C

Proiectarea unui controler VGA simplu în VHDL și Verilog: 5 pași

Proiectarea unui controler VGA simplu în VHDL și Verilog: În acest instructable, vom proiecta un controler VGA simplu în RTL. VGA Controller este circuitul digital conceput pentru a conduce afișaje VGA. Se citește din Frame Buffer (memorie VGA) care reprezintă cadrul care trebuie afișat și generează nece