Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:44.

- Modificat ultima dată 2025-01-23 15:04.

În acest instructable, vom proiecta un controler VGA simplu în RTL. VGA Controller este circuitul digital conceput pentru a conduce afișaje VGA. Se citește din Frame Buffer (memorie VGA) care reprezintă cadrul care trebuie afișat și generează datele necesare și semnale de sincronizare în scopul afișării.

Dacă sunteți în căutarea codului Verilog / System Verilog: Vizitați blogul meu Controller VGA și sistem video în Verilog

Pasul 1: Interfața unui controler VGA

Următoarele sunt principalele semnale de interfață dintr-un controler VGA

- Pixel Clock sau VGA Clock

- Semnalele HSYNC și VSYNC

Pentru afișajul VGA ales, trebuie să calculați mai întâi frecvența ceasului pixel necesar pentru al conduce. Depinde de 3 parametri: Total pixeli orizontali, Total pixeli verticali, Rata de reîmprospătare a ecranului.

De obicei, F = THP * TVP * Rata de reîmprospătare

Găsiți documentația privind ceasul de pixeli necesară pentru diferite afișaje VGA, în RAR atașat.

Semnalele HSYNC și VSYNC sunt generate din ceasul Pixel. Momentul semnalelor HSYNC și VSYNC depinde de numărul de parametri: Frontporch orizontal și vertical, Backporch orizontal și vertical, pixeli de afișare orizontale și verticale, lățimi și polarități ale impulsurilor de sincronizare orizontală și verticală.

Acești parametri sunt standardizați pentru un afișaj VGA ales. Găsiți aceste documente în RAR atașat.

Acești parametri sunt parametri configurabili în controlerul nostru VGA IP.

Pasul 2: Integrarea controlerului VGA cu un afișaj VGA

Figura prezintă modul de integrare a controlerului VGA cu un afișaj VGA. Aveți nevoie de încă două componente pentru a finaliza sistemul:

- Frame Buffer: Memorie care menține cadrul care trebuie afișat.

- Video DAC: DAC care convertește datele digitale RGB și conduce afișajul VGA cu semnale analogice RGB la nivelul de tensiune adecvat.

Unul dintre cele mai simple și populare DAC-uri video este ADV7125. Este un DAC pe 8 biți care convertește cuvintele digitale RGB în semnale analogice 0-0,7 V și conduce afișajul VGA.

Pasul 3: Proiectare tampon cadru

Memoria care „stochează” imaginea care trebuie afișată. Este de obicei o memorie RAM sau uneori ROM. Vom discuta despre cum să proiectăm un buffer de cadre pentru a reprezenta o imagine. Tamponul de cadre transmite aceste informații digitale unui DAC video la comanda de la controlerul VGA.

Mai întâi trebuie să decidem adâncimea pixelilor necesară. Acesta decide calitatea imaginii, varietatea culorilor pe care le poate reprezenta un pixel. Pentru un DAC pe 8 biți, trebuie să reprezentăm componentele de culoare primare ale unui pixel: R, G și B în 8 biți fiecare. Înseamnă că un pixel are 24 de biți.

Fiecare pixel este stocat într-o manieră contiguă în locațiile de memorie Frame Buffer.

Să presupunem că o imagine care trebuie afișată are 800x600 pixeli.

Prin urmare, Frame Buffer necesar este 800x600 = 480000 x 24 biți de memorie

Dimensiunea totală a memoriei este de 800x600x24 = 1400 kB aprox.

Dacă imagine alb-negru, 800x600x1 = 60 kB aprox.

Blocarea RAM poate fi folosită pentru a reprezenta un buffer de cadru în FPGA-urile Xilinx.

Pasul 4: Note

- Sunt necesare semnale suplimentare pe controlerul VGA, în funcție de DAC-ul ales. Am folosit ADV7125.

- Adăugați întârzieri de ciclu prin flip-flops pe VSYNC și HSYNC înainte de a conduce afișajul VGA. Acest lucru se datorează latențelor DAC și Memory. Semnalele pixelilor trebuie sincronizate cu HSYNC și VSYNC. În cazul meu, a fost o întârziere cu 2 cicluri.

- Dacă Frame Buffer de dimensiune dată nu poate fi proiectat pe FPGA din cauza limitării dimensiunii blocului RAM, utilizați memorie mai mică pentru a reprezenta imaginea și pur și simplu editați codul pentru a rula peste adresa de pe limita memoriei disponibile, mai degrabă decât pe marginea întregului cadru. Aceasta va reproduce aceeași imagine de-a lungul întregului ecran. O altă metodă este scalarea pixelilor în care fiecare pixel este reprodus pentru a afișa întreaga imagine pe ecran complet, cu o rezoluție mai mică. Acest lucru se poate face prin modificarea logicii de creștere a adresei în cod.

- Adresa IP este complet portabilă pe toate FPGA-urile și este sincronizată până la 100 MHz pe Virtex-4 FPGA.

Pasul 5: Fișiere atașate

RAR conține:

- Codul controlerului VGA

- PDF-uri ale standardelor VGA.

Recomandat:

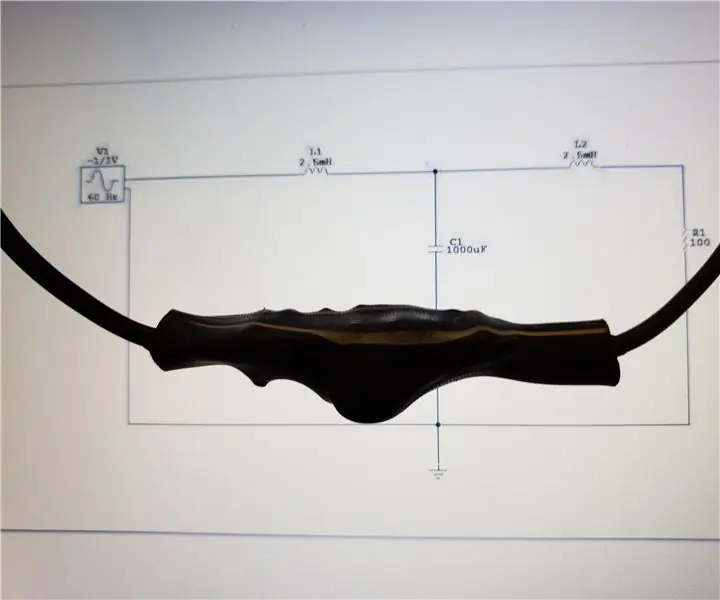

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: 5 pași

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: În acest manual, vă voi arăta cum să luați un cablu USB standard la mini USB, separați-l în mijloc și introduceți un circuit de filtrare care va reduce zgomotul excesiv sau hash produs de o sursă de alimentare tipică pentru Android. Am un portabil m

Proiectarea unui PCB de expansiune (Intel® IoT): 20 de pași

Proiectarea unui PCB de expansiune (Intel® IoT): acest instructabil a fost scris ca punct de plecare pentru cei care sunt dornici să utilizeze Intel® Edison la maximul său potențial, prin încorporarea acestuia într-un proiect încorporat complet dezvoltat. Pentru a face acest lucru, va trebui probabil să faceți - așa cum apelează Intel®

Proiectarea unui controler asociat asociat de cache simplu în patru direcții în VHDL: 4 pași

Proiectarea unui controler de cache asociativ setat în patru direcții în VHDL: În instructajul meu anterior, am văzut cum să proiectăm un controler de cache direct mapat simplu. De data aceasta, facem un pas înainte. Vom proiecta un controler cache asociativ simplu cu patru căi. Avantaj? Mai puțină rata de rate, dar cu prețul perfo

Proiectarea unui controler de întrerupere programabil în VHDL: 4 pași

Proiectarea unui controler de întrerupere programabil în VHDL: sunt copleșit de tipul de răspunsuri pe care le primesc în acest blog. Mulțumesc băieți că mi-ați vizitat blogul și m-ați motivat să vă împărtășesc cunoștințele. De data aceasta, voi prezenta designul unui alt modul interesant pe care îl vedem în toate SOC - Interrupt C

Proiectarea unui controller de cache simplu în VHDL: 4 pași

Proiectarea unui controler de cache simplu în VHDL: scriu acest lucru instructiv, pentru că mi s-a părut puțin dificil să obțin un cod VHDL de referință pentru a învăța și a începe proiectarea unui controler de cache. Așa că am proiectat un controler cache de la zero și l-am testat cu succes pe FPGA. Am p