Cuprins:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:46.

- Modificat ultima dată 2025-01-23 15:04.

Acesta nu este un dispozitiv medical. Aceasta este în scopuri educaționale numai folosind semnale simulate. Dacă utilizați acest circuit pentru măsurători reale ECG, vă rugăm să vă asigurați că circuitul și conexiunile circuit-instrument folosesc tehnici de izolare adecvate

Scopul acestui proiect este de a construi un circuit care poate amplifica și filtra un semnal ECG, cunoscut și sub numele de electrocardiogramă. Un ECG poate fi utilizat pentru a determina ritmul cardiac și ritmul cardiac, deoarece este capabil să detecteze semnalele electrice care trec prin diferite părți ale inimii în timpul diferitelor etape ale ciclului cardiac. Aici folosim un amplificator de instrumentație, un filtru de notch și un filtru trece jos pentru a amplifica și filtra ECG. Apoi, folosind LabView, se calculează ritmurile pe minut și se afișează o reprezentare grafică a ECG. Produsul finit poate fi văzut mai sus.

Pasul 1: Amplificator de instrumentație

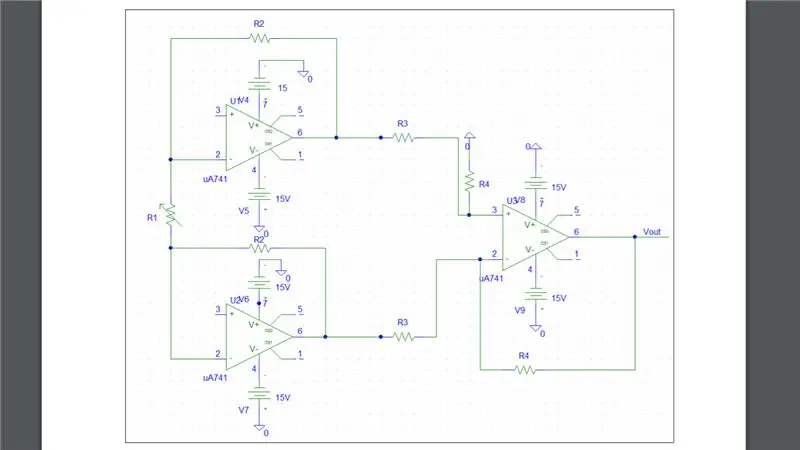

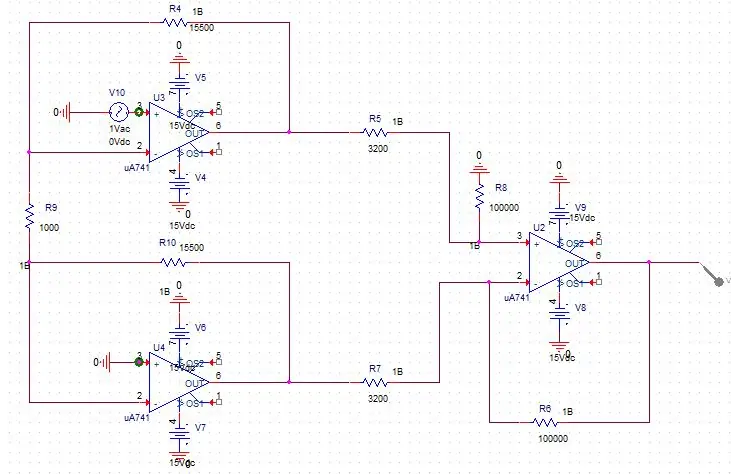

Câștigul necesar pentru amplificatorul de instrumentație este de 1000 V / V. Acest lucru ar permite o amplificare suficientă a semnalului de intrare care este mult mai mică. Amplificatorul de instrumentație este împărțit în două părți, Etapa 1 și Etapa 2. Câștigul fiecărei etape (K) ar trebui să fie similar, astfel încât atunci când este multiplicat împreună, câștigul este în jur de 1000. Ecuațiile de mai jos sunt folosite pentru a calcula câștigul.

K1 = 1 + ((2 * R2) / R1)

K2 = -R4 / R3

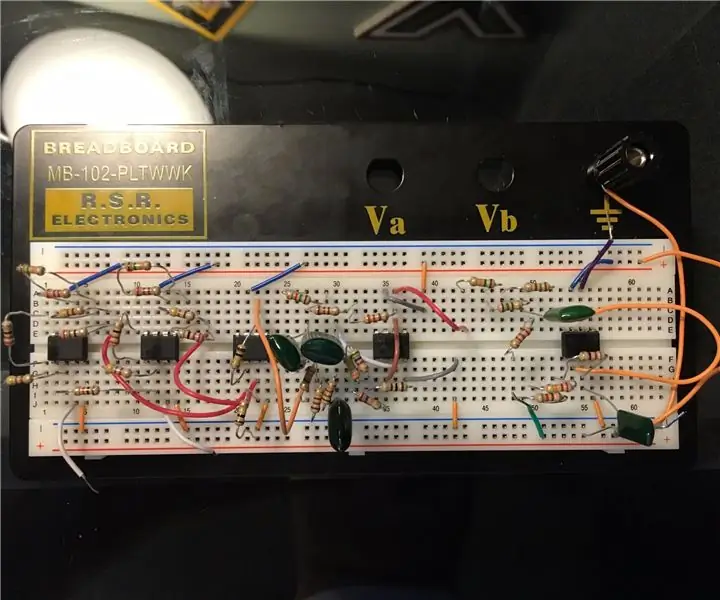

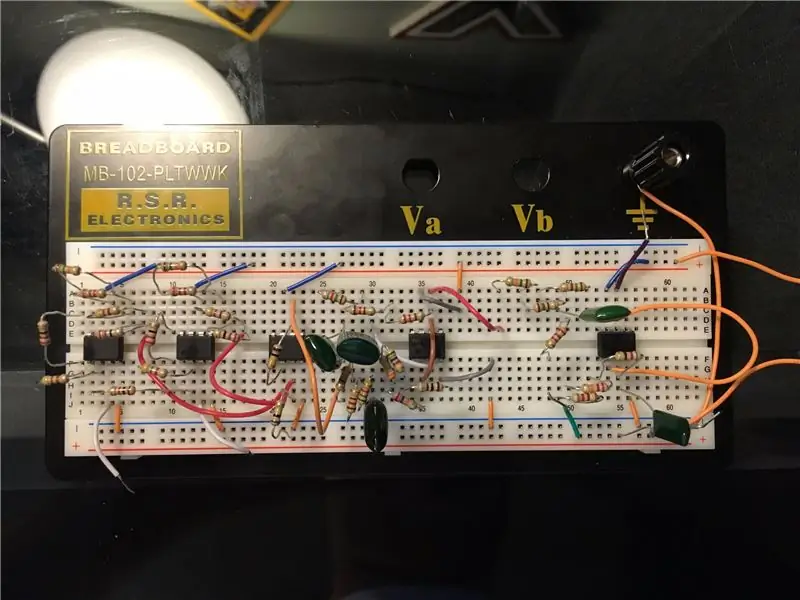

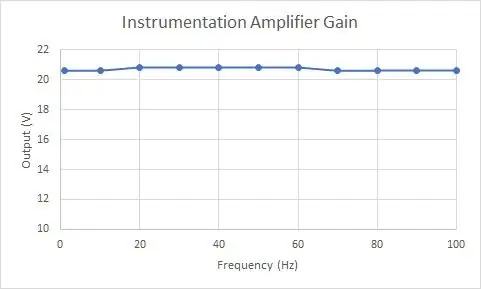

Din aceste ecuații s-au găsit valorile lui R1, R2, R3 și R4. Pentru a construi circuitul văzut în imagini, au fost utilizate trei amplificatoare operaționale și rezistențe uA741. Amplificatoarele de operare sunt alimentate cu 15V de la o sursă de curent continuu. Intrarea amplificatorului de instrumentație a fost conectată la un generator de funcții, iar ieșirea a fost conectată la un osciloscop. Apoi, s-a luat o curgere alternativă și s-a găsit câștigul amplificatorului de instrumentație, așa cum se poate vedea pe graficul "Instrumentation Amplifier Gain" de mai sus. În cele din urmă, circuitul a fost recreat în LabView, unde a fost rulată o simulare a câștigului, așa cum se poate vedea în graficul negru de mai sus. Rezultatele au confirmat că circuitul a funcționat corect.

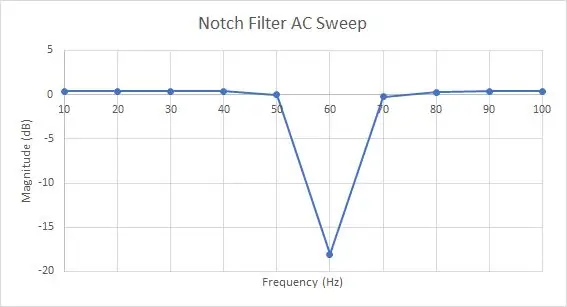

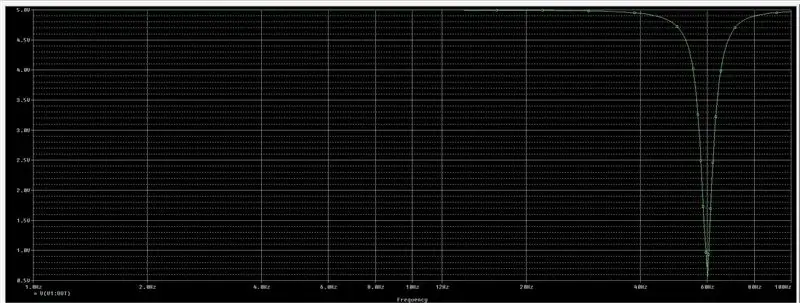

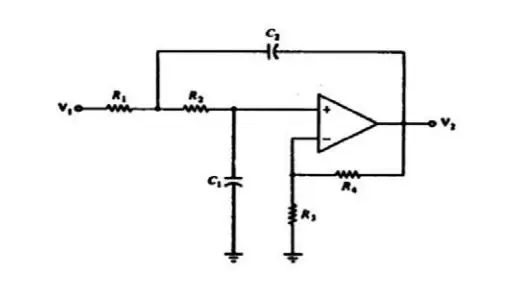

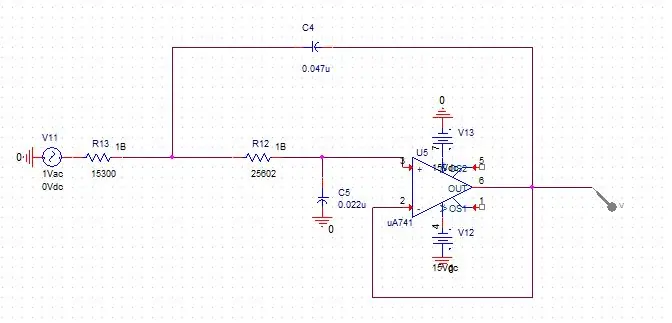

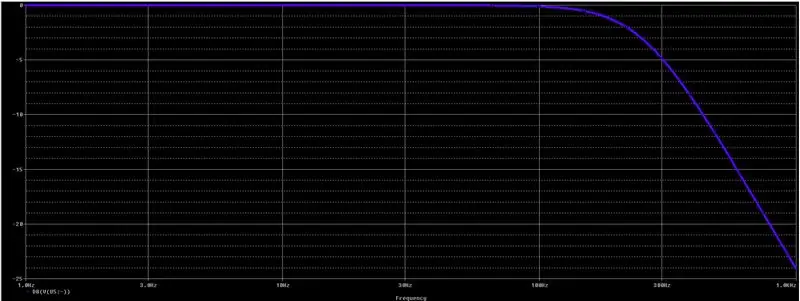

Pasul 2: Filtru de notch

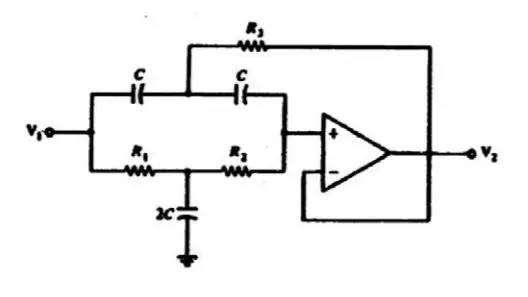

Filtrul cu crestături este utilizat pentru a elimina zgomotul care apare la 60 Hz. Valorile componentelor pot fi calculate folosind ecuațiile de mai jos. A fost utilizat un factor de calitate (Q) de 8. C a fost ales având în vedere condensatorii disponibili.

R1 = 1 / (2 * Q * ω * C)

R2 = 2 * Q / (ω * C)

R3 = (R1 * R2) / (R1 + R2)

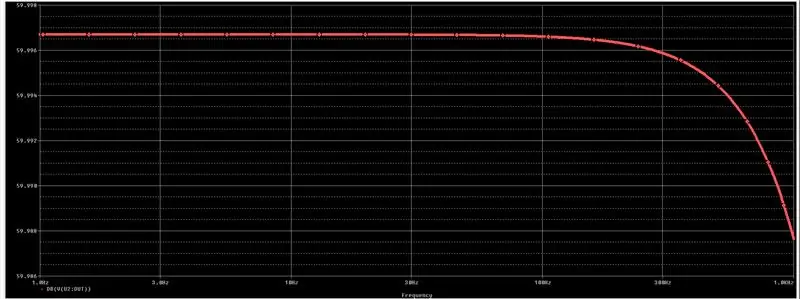

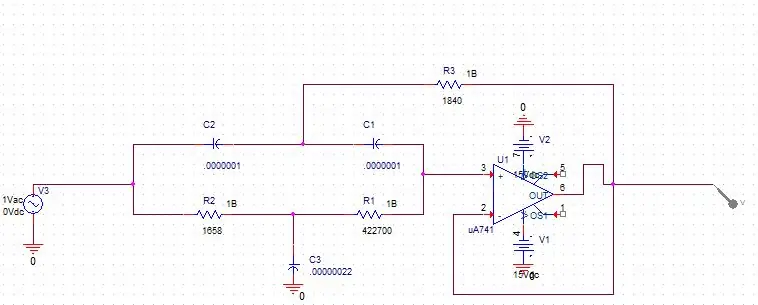

Valorile rezistenței și ale condensatorului au fost găsite și circuitul de mai sus a fost construit, valorile calculate pot fi văzute acolo. Amplificatorul operațional a fost alimentat de o sursă de curent continuu, cu intrarea conectată la un generator de funcții și ieșirea la un osciloscop. Rularea unui AC Sweep a dus la graficul "Notch Filter AC Sweep" de mai sus, arătând că o frecvență de 60 Hz a fost eliminată. Pentru a confirma acest lucru, a fost rulată o simulare LabView care a confirmat rezultatele.

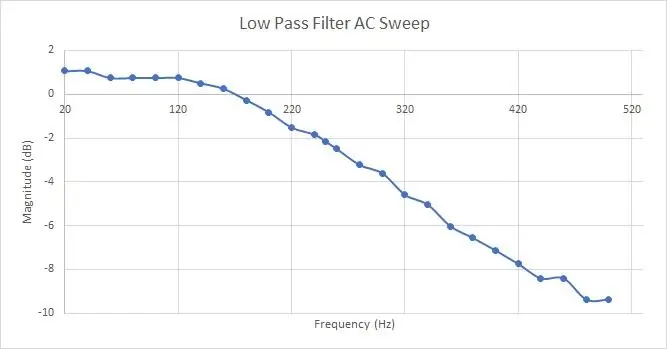

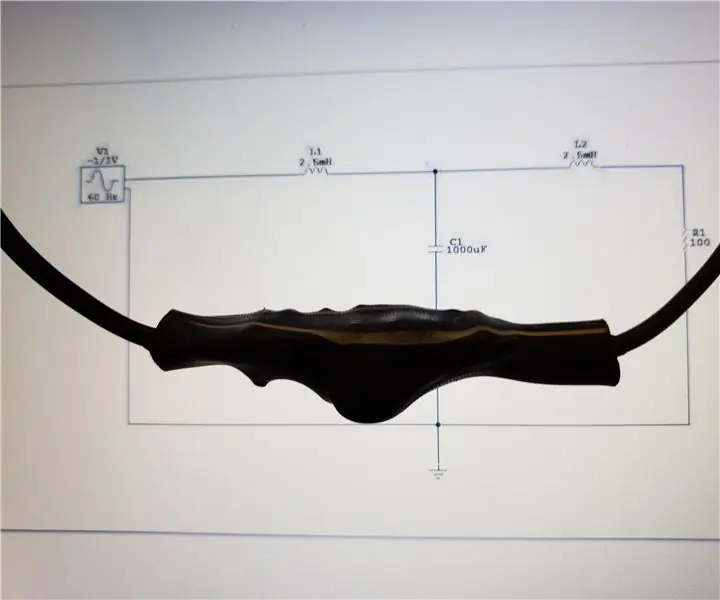

Pasul 3: Filtru de trecere redusă

Se folosește un filtru trece jos Butterworth de ordinul doi, cu o frecvență de întrerupere de 250Hz. Pentru a rezolva valorile rezistorului și condensatorului, au fost utilizate ecuațiile de mai jos. Pentru aceste ecuații, frecvența de întrerupere în Hz a fost modificată pentru a fi în rad / sec, care s-a dovedit a fi 1570,8. S-a folosit un câștig de K = 1. Valorile pentru a și b au fost furnizate să fie 1.414214 și respectiv 1.

R1 = 2 / (wc (a C2 + sqrt (a ^ 2 + 4 b (K - 1)) C2 ^ 2 - 4 b C1 C2))

R2 = 1 / (b C1 C2 R1 wc ^ 2)

R3 = K (R1 + R2) / (K - 1)

R4 = K (R1 + R2)

C1 = (C2 (a ^ 2 + 4 b (K-1)) / (4 b)

C2 = (10 / fc)

Odată ce valorile au fost calculate, circuitul a fost construit cu valorile, care pot fi văzute într-una dintre imaginile de mai sus. Trebuie remarcat faptul că, deoarece a fost utilizat un câștig de 1, R3 a fost înlocuit cu un circuit deschis și R4 a fost înlocuit cu un scurtcircuit. Odată ce circuitul a fost asamblat, atunci amplificatorul operațional a fost alimentat cu 15V de la o sursă de alimentare DC. Similar cu celelalte componente, intrarea și ieșirea au fost conectate la un Generator de funcții și respectiv la un osciloscop. A fost creat un grafic al curățării de curent alternativ, văzut în „Filtru de trecere redusă CA de curățare” de mai sus. Graficul în negru în simularea circuitului LabView, confirmând rezultatele noastre.

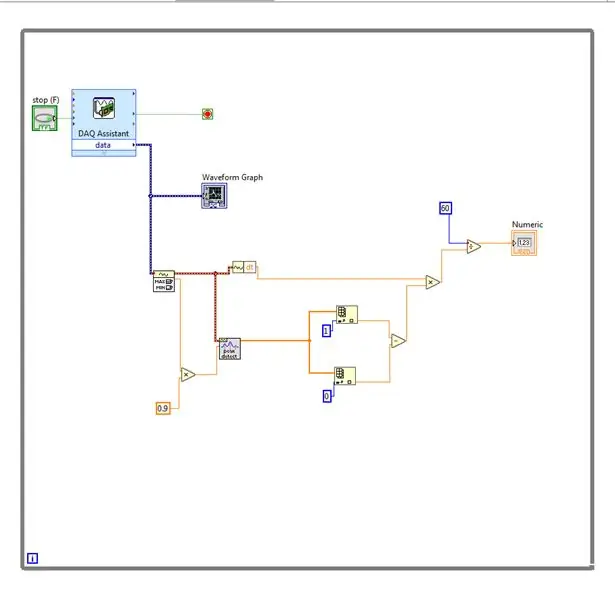

Pasul 4: LabVIEW

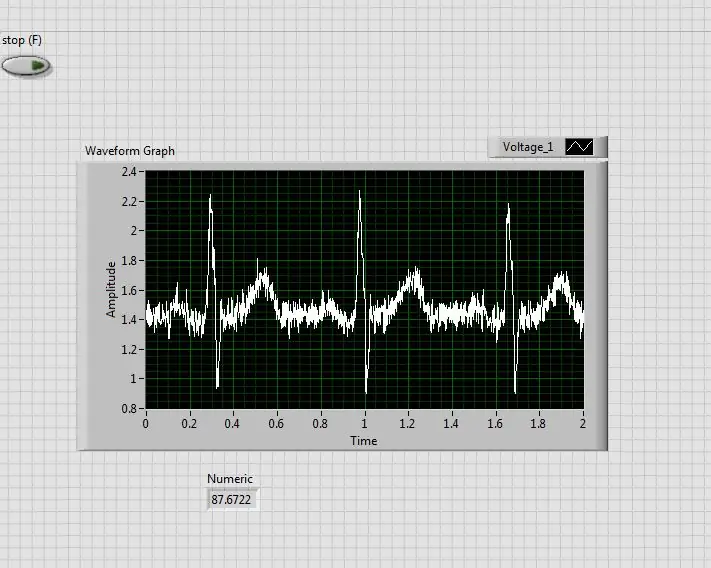

Programul LabVIEW prezentat în imagine este utilizat pentru a calcula bătăile pe minut și pentru a afișa o reprezentare vizuală a ECG de intrare. Asistentul DAQ capătă semnalul de intrare și setează parametrii de eșantionare. Graficul de formă de undă trasează apoi intrarea pe care DAQ o primește pe interfața de utilizare pentru a o afișa utilizatorului. Analizele multiple se fac pe datele de intrare. Valorile maxime ale datelor de intrare se găsesc utilizând identificatorul Max / Min, iar parametrii pentru detectarea vârfurilor sunt setați utilizând Detectarea vârfurilor. Folosind o matrice de indexuri a locațiilor vârfurilor, timpul dintre valorile maxime date de componenta Change in Time și diverse operații aritmetice, BPM este calculat și afișat ca ieșire numerică.

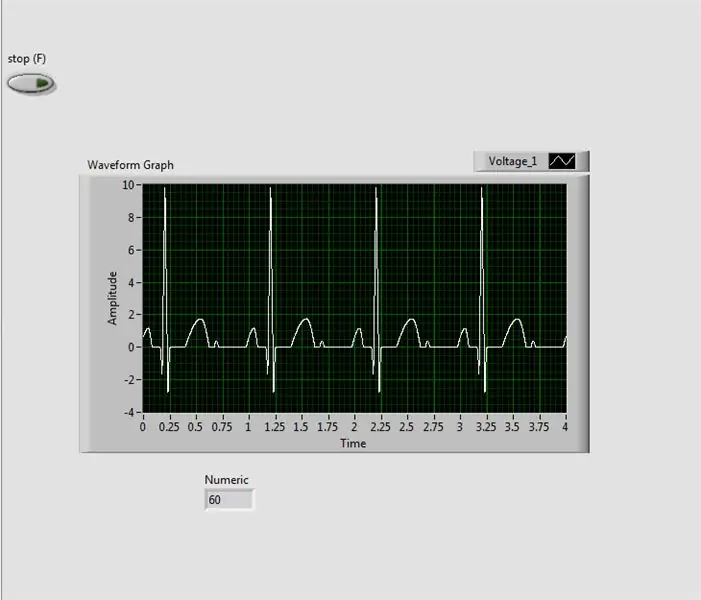

Pasul 5: Circuitul finalizat

Odată ce toate componentele au fost conectate, sistemul complet a fost testat cu un semnal ECG simulat. Apoi, circuitul a fost utilizat pentru a filtra și amplifica un ECG uman cu rezultatele afișate prin programul LabView menționat anterior. Electrozii au fost atașați la încheietura mâinii drepte, la încheietura stângă și la glezna stângă. Încheietura stângă și încheietura dreaptă au fost conectate la intrările amplificatorului de instrumentație, în timp ce glezna stângă a fost conectată la sol. Ieșirea filtrului trece jos a fost apoi conectată la DAQ Assistant. Folosind aceeași diagramă bloc LabView dinainte, programul a fost rulat. Odată cu trecerea ECG umană, un semnal clar și stabil a fost văzut de la ieșirea sistemului complet, care poate fi văzut în imaginea de mai sus.

Recomandat:

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: 5 pași

Proiectarea și construirea unui filtru de linie de alimentare pentru un încărcător de telefon Android: În acest manual, vă voi arăta cum să luați un cablu USB standard la mini USB, separați-l în mijloc și introduceți un circuit de filtrare care va reduce zgomotul excesiv sau hash produs de o sursă de alimentare tipică pentru Android. Am un portabil m

Proiectarea unui PCB de expansiune (Intel® IoT): 20 de pași

Proiectarea unui PCB de expansiune (Intel® IoT): acest instructabil a fost scris ca punct de plecare pentru cei care sunt dornici să utilizeze Intel® Edison la maximul său potențial, prin încorporarea acestuia într-un proiect încorporat complet dezvoltat. Pentru a face acest lucru, va trebui probabil să faceți - așa cum apelează Intel®

Proiectarea unui controler asociat asociat de cache simplu în patru direcții în VHDL: 4 pași

Proiectarea unui controler de cache asociativ setat în patru direcții în VHDL: În instructajul meu anterior, am văzut cum să proiectăm un controler de cache direct mapat simplu. De data aceasta, facem un pas înainte. Vom proiecta un controler cache asociativ simplu cu patru căi. Avantaj? Mai puțină rata de rate, dar cu prețul perfo

Proiectarea unui controler de întrerupere programabil în VHDL: 4 pași

Proiectarea unui controler de întrerupere programabil în VHDL: sunt copleșit de tipul de răspunsuri pe care le primesc în acest blog. Mulțumesc băieți că mi-ați vizitat blogul și m-ați motivat să vă împărtășesc cunoștințele. De data aceasta, voi prezenta designul unui alt modul interesant pe care îl vedem în toate SOC - Interrupt C

Proiectarea unui controller de cache simplu în VHDL: 4 pași

Proiectarea unui controler de cache simplu în VHDL: scriu acest lucru instructiv, pentru că mi s-a părut puțin dificil să obțin un cod VHDL de referință pentru a învăța și a începe proiectarea unui controler de cache. Așa că am proiectat un controler cache de la zero și l-am testat cu succes pe FPGA. Am p