Cuprins:

- Pasul 1: Construirea unui modul PWM - fișier sursă

- Pasul 2: Construirea unui modul PWM - Configurare Vivado

- Pasul 3: Construirea unui modul PWM - Creați un fișier de proiect

- Pasul 4: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (I)

- Pasul 5: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (II)

- Pasul 6: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (III)

- Pasul 7: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (IV)

- Pasul 8: Construirea unui modul PWM - Designul blocului și setarea fișierului de constrângere (V)

- Pasul 9: Construirea unui modul PWM - Instalare hardware

- Pasul 10: Construirea unui modul PWM - Generați Bitstream și lansați SDK

- Pasul 11: Construirea unui modul PWM - Creați o aplicație nouă în Xilinx SDK

- Pasul 12: Construirea unui modul PWM - Prezentare generală a Explorerului de proiect (I)

- Pasul 13: Construirea unui modul PWM - Prezentare generală a Project Explorer (II)

- Pasul 14: Construirea unui modul PWM - Prezentare generală a Exploratorului de proiecte (III)

- Pasul 15: Construirea unui modul PWM - Funcția de încheiere PWM (I)

- Pasul 16: Construirea unui modul PWM - Funcția de încheiere PWM (II)

- Pasul 17: Construirea unui modul PWM - Funcția de încheiere PWM (III)

- Pasul 18: Construirea unui modul PWM - Fă-l rula

- Pasul 19: Procesare video în flux pe Digilent ZYBO cu OV7670

- Pasul 20: Completați diagrama bloc

- Pasul 21: Conectați OV7670 la ZYBO

- Pasul 22: Creați design de bloc

- Pasul 23: Adăugați fișiere VHDL pentru controlul și captura camerei OV7670

- Pasul 24: Adăugați fișierul de constrângeri

- Pasul 25: Adăugați IP Repo pentru IP HLS

- Pasul 26: Adăugați module și IP

- Pasul 27: Setări de configurare IP

- Pasul 28: Adăugați și configurați blocul PS IP

- Pasul 29: Partea 1. Construirea unui modul PWM pentru servomotoare

- Pasul 30: Conexiuni laterale de intrare video (aclk Evidențiat)

- Pasul 31: Conexiuni la OV7670

- Pasul 32: Conexiuni pe partea de ieșire video

- Pasul 33: Rulați blocarea și automatizarea conexiunii

- Pasul 34: Generați HDL Wrapper

- Pasul 35: Generați Bitstream, Exportați hardware în SDK, Lansați SDK de la Vivado

- Pasul 36: SDK (fără FreeRTOS)

- Pasul 37: Implementarea FreeRTOS

- Pasul 38: Instrucțiuni de utilizare

- Pasul 39: Referințe și linkuri

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:46.

- Modificat ultima dată 2025-01-23 15:04.

Începeți la primul pas pentru detalii despre crearea unui controler servo PWM pe 2 axe.

Începeți de la diagrama bloc masivă (Pasul 19) pentru întregul proiect.

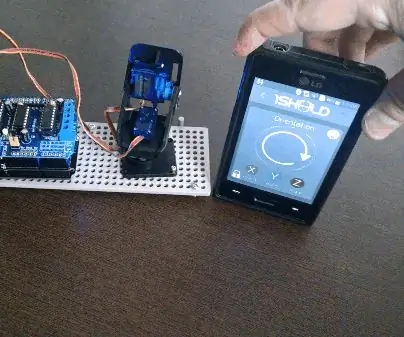

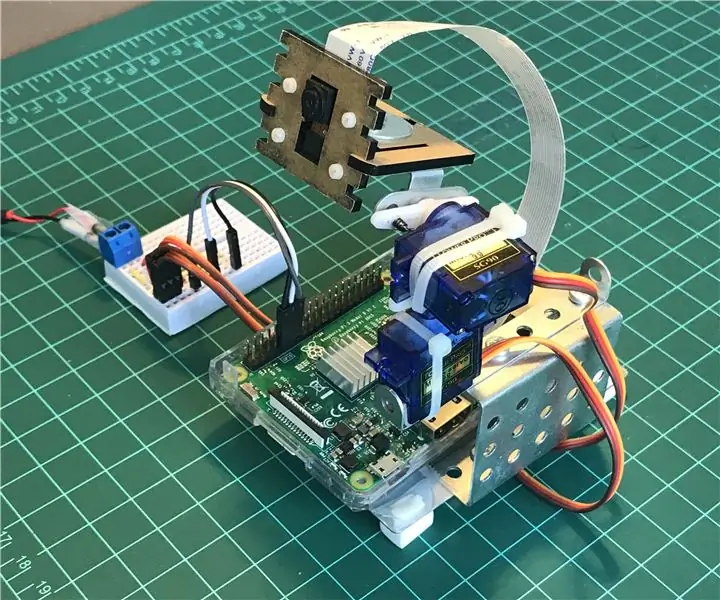

Configurare cameră + panoramare / înclinare pe care am folosit-o:

PmodCON3 de la Digilent a fost folosit pentru a conecta servo-urile.

Pasul 1: Construirea unui modul PWM - fișier sursă

Pasul 2: Construirea unui modul PWM - Configurare Vivado

Mai întâi, descărcați Vivado Design Suite De pe site-ul Xilinx. Instalați toată suita de design, inclusiv Vivado Software Development Kit (SDK). Acest proiect folosește versiunea 2017.2.

Între timp, Digilent Adept 2 ar trebui instalat și ca driver de placă Zybo.

Pasul 3: Construirea unui modul PWM - Creați un fișier de proiect

Înainte de a crea un fișier de proiect, ar trebui să vă asigurați că ați instalat deja fișierul Zybo corect ca tutorial aici:

Versiunea Vivado 2015.1 și ulterior Instalarea fișierului de bord

Deschide Vivado 2017.2. În Quick Start, faceți clic pe Creare proiect -> Următor -> Nume proiect (denumiți numele proiectului aici) -> Tipul proiectului. Pe Project Type, selectați RTL Project și marcați „Nu specificați sursele în acest moment”. Apoi, pentru partea implicită, selectați „Panouri” și „Zybo” ca nume afișat. Apoi, faceți clic pe Finalizare pentru a începe proiectul.

Pasul 4: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (I)

În Flow Navigator, faceți clic pe „” Create Block Design”, apoi apăsați OK. faceți clic pe semnul „+” pentru a adăuga adresele IP necesare. Adăuga:

- Un sistem de procesare ZYNQ7 Two AXI Timer

- Două temporizatoare AXI

Pasul 5: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (II)

După adăugarea adreselor IP, executați automatizarea blocului și automatizarea conexiunii. Odată finalizată automatizarea, pe blocul „axi_timer_0”, faceți clic dreapta pe pwm0 -> Make External. Denumiți pinul extern pwm0 ca pwm_Xaxis. De asemenea, repetați procesul de mai sus pe blocul „axi_timer_1” și denumiți pinul extern pwm0 ca pwm_Zaxis.

Pasul 6: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (III)

Observați că de fiecare dată când terminăm Block Design-ul în Vivado, trebuie să creăm un HDL Wrapper. Deoarece va fi modulul de nivel superior pentru fiecare proiect.

Pasul 7: Construirea unui modul PWM - Proiectarea blocurilor și setarea fișierului de constrângere (IV)

Acum, trebuie să configurăm fișierul nostru de constrângere pentru a atribui pini conectați la diagrama noastră bloc. Închideți fereastra Block Design, pe fila Surse, „Adăugați surse” -> Adăugați sau creați constrângeri-> adăugați Zybo-Master.xdc ca fișiere de constrângere.

Pasul 8: Construirea unui modul PWM - Designul blocului și setarea fișierului de constrângere (V)

Deschideți fișierul de constrângere Zybo-Master.xdc din folderul Constraints, decomentați porturile pe care dorim să le specificăm ca semnale de ieșire și redenumiți „get_ports {XXXX}”, care XXXX denotă pinul extern denumit în diagrama bloc. Setarea fișierului de constrângere este prezentată în figură.

Pasul 9: Construirea unui modul PWM - Instalare hardware

Conectați servomotorele la Pmod CON3. TowerPro SG90 este modelul de servomotor pe care l-am folosit în acest proiect. Pentru firele servomotorului, firul portocaliu reprezintă semnalul PWM, conectat la pinul SIG în Pmod CON3. Firul roșu Vcc este un fir de alimentare conectat la pinul VS în Pmod CON3. În cele din urmă, firul maro Gnd este un fir de împământare conectat la pinul GND. Apoi, introduceți Pmod CON3 în rândul superior al portului JD în placa Zybo.

Pasul 10: Construirea unui modul PWM - Generați Bitstream și lansați SDK

1. În fila Project Navigator, rulați Generați BitStream.

2. Exportați hardware: Fișier> Export> Exportare hardware-> marcați pe „include bitstream” -> OK 3. Lansați SDK: Fișier -> Lansați SDK.

Pasul 11: Construirea unui modul PWM - Creați o aplicație nouă în Xilinx SDK

Creați o aplicație nouă:

Fișier> Nou> Aplicație -> Introduceți numele proiectului dvs. -> Finalizare

În Project Explorer, ar trebui să existe trei foldere.

În acest caz, „design_1_wrapper_hw_platform_0” este folderul exportat anterior de Vivado. Axis_2_PWM_SDK_bsp este folderul pachetului de asistență al plăcii. Și Axis_2_PWM_SDK este folderul nostru principal de proiect în SDK. Puteți vedea fișierul „helloworld.c” în dosarul „src” al Axis_2_PWM_SDK, unde „helloworld.c” este fișierul principal.

Pasul 12: Construirea unui modul PWM - Prezentare generală a Explorerului de proiect (I)

Să verificăm câteva fișiere în Project Explorer. Mai întâi, în folderul „design_1_wrapper_hw_platform_0”, deschideți „system.hdf”. Acest fișier demonstrează harta de adrese pentru procesorul ps7_cortex9 și blocurile IP prezente în proiectarea noastră.

Pasul 13: Construirea unui modul PWM - Prezentare generală a Project Explorer (II)

Apoi, verificați fișierele „include” și „libsrc” din folderul „Axis_2_PWM_SDK_bsp”. Fișierele bibliotecii de aici ne permit să interacționăm cu periferice hardware fără a „juca” registre.

Pasul 14: Construirea unui modul PWM - Prezentare generală a Exploratorului de proiecte (III)

Prin documentația BSP, xtmrctr.h este găsit ca o bibliotecă de control Xilinx Timer legată de AXI Timer. De obicei, am putea găsi funcția PWM dorită aici. Cu toate acestea, dacă citiți documentația „tmrctr_v4_3”, arată că driverul nu acceptă în prezent funcționarea PWM a dispozitivului. Datorită deficienței funcției PWM, trebuie să încheiem funcția PWM cu ajutorul ghidului produsului xtmrctr.h și AXI Timer v2.0 LogiCORE IP.

Pasul 15: Construirea unui modul PWM - Funcția de încheiere PWM (I)

Înapoi la fișierul principal „helloworld.c”, includeți următoarele fișiere antet:

Pasul 16: Construirea unui modul PWM - Funcția de încheiere PWM (II)

Definiți adresele de bază ale două AXI TImer prin „xparameters.h”.

Pasul 17: Construirea unui modul PWM - Funcția de încheiere PWM (III)

Construiți funcția PWM dorită.

Duty_val: convertește valoarea gradului în ciclu de funcționare. PWM_Freq_Duty: setați frecvența și ciclul de funcționare dorite pentru a genera PWM. Perioada de ceas ar trebui, de asemenea, să fie alocată.

PWM_START: atribuiți adresa de înregistrare PWM și începeți să generați PWM.

PWM_STOP: atribuiți adresa de înregistrare PWM și opriți generarea PWM.

Restul codului demonstrativ este afișat în „helloworld.c” sub „Axis_2_PWM_SDK”

Pasul 18: Construirea unui modul PWM - Fă-l rula

1. Programați FPGA prin SDK

- Conectați placa Zybo prin portul USB la computer.

- Instrumente Xilinx -> Program FPGA

2. Rulați programul

Faceți clic pe pictograma „Run” și derulați meniul -> Run As -> Launch on Hardware

3. Terminal SDK

- Deschideți terminalul SDK -> Conectați-vă la portul serial -> OK

- Rulați programul. Dacă codul demonstrativ rulează cu succes, ar trebui să vedeți „Initializarea a fost finalizată!” pe terminalul SDK.

Pasul 19: Procesare video în flux pe Digilent ZYBO cu OV7670

Fișier complet de arhivă atașat.

Pasul 20: Completați diagrama bloc

Aceasta arată schema completă a tuturor conexiunilor și blocurilor IP din proiect

Pasul 21: Conectați OV7670 la ZYBO

Creați o conexiune pentru a conecta modulul ov7670 la ZYBO Pmods

Data Pmod este Pmod D.

Controlul Pmod este Pmod C

În plus, conectați PmodCON3 și serv-urile așa cum se specifică în prima jumătate a acestui tutorial

Pasul 22: Creați design de bloc

În Flow Navigator, faceți clic pe „Create Block Design”, apoi apăsați OK.

Pasul 23: Adăugați fișiere VHDL pentru controlul și captura camerei OV7670

Adăugați fișierele VHDL atașate acestui pas la proiect

Pasul 24: Adăugați fișierul de constrângeri

Adăugați fișierul de constrângeri atașat la proiect.

Pasul 25: Adăugați IP Repo pentru IP HLS

Luați fișierul Zip atașat și dezarhivați-l într-un folder nou denumit similar într-un nou director (folder) numit „HLS_repo”.

Adăugați un depozit IP la proiectul dvs. accesând catalogul IP și făcând clic dreapta selectând „Adăugare depozit…”

Navigați la directorul „HLS_repo” și selectați-l.

Opțional: creați singur blocul de procesare video HLS!

Pasul 26: Adăugați module și IP

Adăugați modulele ov7670_axi_stream_capture, debounce și ov7670_controller la diagrama bloc făcând clic dreapta pe fundal și selectând „Adăugați modul …”

În mod similar, adăugați adresele IP:

- HLS_Video_Track

- Scriere tampon cadru video

- Citire tampon cadru video

- Controler de sincronizare video

- AXI4-Stream către ieșire video

- 3 din „felie”

- Constant

- 2 din AXI Timer

Pasul 27: Setări de configurare IP

Așa cum se arată în imagini

Pasul 28: Adăugați și configurați blocul PS IP

Adăugați sistemul de procesare ZYNQ7 la diagrama bloc

editați configurația:

-

Configurare PS-PL

-

HP

- Activați S HP 0

- Activați S HP 1

-

-

Configurarea ceasului

-

PL Ceasuri din stofă

- FCLK_0 la 100MHz

- FCLK_1 la 25 MHz (OutputClock)

- FLCK_2 la 35MHz (<= 50MHz) (CameraClock)

-

Pasul 29: Partea 1. Construirea unui modul PWM pentru servomotoare

Aduceți axi_timer_0 pwm0 la noul port de ieșire pwm_Xaxis

Aduceți axi_timer_1 pwm0 la noul port de ieșire pwm_Zaxis

Pasul 30: Conexiuni laterale de intrare video (aclk Evidențiat)

Conectați corect blocurile IP din partea de intrare video

(* aceste conexiuni ar trebui create prin selectarea opțiunilor corecte în timpul automatizării conexiunii) "aclk" din axi_stream_capture merge la:

- ap_clk pe scriere tampon cadru video

- ap_clk pe blocul de procesare a fluxului video HLS

- * faceți clic pe IP AXI smartconnect din bufferul cadru video Scrieți în S_AXI_HP0

- * aclk corespunzător canalelor IP de interconectare AXI pentru canalele S_AXI ale blocului de procesare video HLS și tamponul cadrului video scrie S_AXI_HP0_ACLK pe blocul PS

Semnalul fluxului video este pur și simplu conectat în serie de la blocul de captură la interfața de memorie Zynq.

- Videoclipul trece de la blocul de captură la blocul de procesare HLS.

- Videoclipul procesat din blocul HLS merge la blocul de scriere a bufferului de cadre.

- * Blocul de scriere tampon cadru se conectează la interfața HP0 de pe blocul Zynq PS.

- Semnalul m_axis_tuser de la ieșirea blocului de captură este conectat manual atât la semnalul de intrare video_in_TUSER de pe blocul de procesare HLS, cât și la semnalul ap_start de pe același bloc.

Semnalul TUSER (tuser) este utilizat de protocolul de flux video AXI pentru a indica începutul unui cadru al videoclipului. AP_Start spune blocului HLS să înceapă procesarea. Prin urmare, folosim tuser pentru a declanșa blocul HLS pentru a procesa fiecare cadru așa cum este intră. Când conectați un singur semnal al unui autobuz și îl împărțiți în acest mod, este necesar să îl conectați și la punctul de terminare normal al restului autobuzului. Vivado presupune că, dacă conectați manual semnalul, doriți să deconectați la ce s-ar conecta în mod normal.

Setări de configurare a blocurilor IP:

Scriere tampon cadru video:

Formate video: RGB8

1 eșantion pe ceas Max. Coloane: 1280 (> = 640) Max rânduri: 960 (> = 480) Lățimea maximă a datelor: 8

Pasul 31: Conexiuni la OV7670

Pe blocul ov7670_axi_stream_capture

- Faceți toate intrările externe (faceți clic dreapta pe un pin și selectați din meniu sau faceți clic stânga-> ctrl + T)

- Lăsați numele așa cum sunt

Pe blocul ov7670_controller

- Faceți toate ieșirile de bloc externe

- Redenumiți portul config_finished în led0

- conectați clk la CameraClock (<= 50MHz) (FCLK_2)

Pe blocul debounce

- conectați butonul de intrare 1 la un port de intrare extern numit btn0

- conectați ieșirea 1 la linia de retransmisie de pe blocul IP ov7670_controller

- conectați intrarea button2 la un port de intrare extern numit btn3

- conectați out2n la intrarea ext_reset_in de pe sistemul Procesor Reset IP pentru domeniul ceasului de captură video. (* Acest lucru poate fi necesar să se facă după generarea acelui IP *)

- conectați clk la CameraClock (<= 50MHz) (FCLK_2)

Pasul 32: Conexiuni pe partea de ieșire video

Conexiuni pentru blocuri Video Timing Controller (VTC), AXI4-Stream to Video Out și felii

- Utilizați ceasul de 25 MHz (FCLK_1) pentru vid_io_out_clk și VTC clk

- Folosiți ceasul de 100 MHz (FCLK_0) pentru aclk pe AXI4-Stream to Video Out

- vtiming_out la vtiming_in

- Citire tampon cadru video m_axis_video merge la AXI4-Stream to Video Out video_in

- vtg_ce merge la gen_clken

- Legați VTC clken, aclken, vid_io_out_ce la Constant dout [0: 0]

- Aduceți vid_hsync și vid_vsync în porturile de ieșire externe vga_hs și, respectiv, vga_vs. (nu este ilustrat)

Felii:

-

Feliile trebuie configurate așa cum se arată în imaginile atașate

- redenumiți blocurile în slice_red, slice_green și slice_blue

- configurați intervalele de felii așa cum se arată în imagini în funcție de numele blocului

- conectați fiecare ieșire felie la o ieșire de port extern așa cum se arată în imagine.

- vid_data [23: 0] se conectează la intrările pentru fiecare felie (Din [23: 0])

Pasul 33: Rulați blocarea și automatizarea conexiunii

Rulați Block Automation pentru a conecta lucrurile din blocul ZYNQ7 PS. După cum arată imaginea.

Rulați automatizarea conexiunii pentru a crea toate IP-urile de interconectare. Acordați o atenție deosebită tuturor opțiunilor din fiecare imagine.

Pe blocul de retragere, conectați out2n la domeniul ceasului de captură video Procesor Resetare sistem Ext_reset_in input.

Pasul 34: Generați HDL Wrapper

Generați învelișul HDL pentru designul blocului.

Setați-l ca modul superior.

Pasul 35: Generați Bitstream, Exportați hardware în SDK, Lansați SDK de la Vivado

Asigurați-vă că includeți fluxul de biți în export.

Generarea fluxului de biți poate dura foarte mult.

Apoi lansați SDK

Pasul 36: SDK (fără FreeRTOS)

Această versiune face totul fără a utiliza FreeRTOS, condensând codul frumos.

Creați un BSP independent pe baza designului hardware. Opțiunile implicite ar trebui să fie în regulă. Asigurați-vă că au fost generate surse BSP.

Creați aplicația așa cum se arată în imagine. (aplicație goală)

Ștergeți principalul generat automat și importați fișierele atașate.

Pasul 37: Implementarea FreeRTOS

Această versiune folosește FreeRTOS. Creați un FreeRTOS901 BSP bazat pe designul hardware. Opțiunile implicite ar trebui să fie în regulă. Asigurați-vă că au fost generate surse BSP.

Creați aplicația așa cum se arată în imagine. (aplicație goală)

Ștergeți principalul generat automat și importați fișierele atașate.

Pasul 38: Instrucțiuni de utilizare

Acest proiect este un pic dificil pentru a rula. Urmați pașii în ordine.

Asigurați-vă că dispozitivul dvs. ZYBO nu se autoîncarcă nimic atunci când este pornit. Aceasta înseamnă că LED-ul Gata nu ar trebui să se aprindă. O modalitate de a face acest lucru este să setați jumper-ul sursei de boot la JTAG.

Deschideți proiectul (FreeRTOS sau nu) pe care doriți să îl programați din SDK

- Porniți ZYBO. LED-ul Terminat nu ar trebui să se aprindă.

- Programați FPGA cu fișierul bit. LED-ul Gata ar trebui să se aprindă. Led0 nu ar trebui să se aprindă.

- Rulați codul (nu uitați să treceți de punctul de întrerupere de pornire dacă faceți acest lucru).

În acest moment ar trebui să obțineți o ieșire pe afișajul dvs. VGA.

Pentru a reporni (dacă are probleme sau orice altceva): atingeți rapid butonul PS-SRST sau opriți ZYBO și apoi reporniți-l. Continuați de la pasul 2.

Întreruperea procesorului cu depanatorul va determina aparatul să mențină poziția în loc să se miște. Fluxul video va continua oricum.

Pasul 39: Referințe și linkuri

Ghiduri și documentație de referință Xilinx:

- PG044 - Stream AXI la ieșire video

- PG278 - Citire / Scriere tampon cadru video

Alte legături:

- Blogul lui Lauri - intrare VDMA

- Blogul lui Lauri - ieșire OV7670 la VGA folosind BRAM

- Wiki Hamsterworks, de Mike Fields, sursa originală a codului OV7670

- Foaie de date care prezintă specificațiile de timp de bază

Recomandat:

Pan Tilt controlat de telefonul mobil: 4 pași

Pan Tilt controlat de telefonul mobil: Bună ziua tuturor, în noul meu proiect vă voi prezenta un Pan-Tilt controlat de telefonul mobil. Toate mișcările telefonului mobil sunt reproduse în dispozitivul pan-tilt prin Bluetooth. Construcția este foarte simplu folosind un Arduino R3 (sau similar) și tw

Mecanism Pan și Tilt pentru DSLR Time Lapses: 7 pași (cu imagini)

Mecanismul Pan și Tilt pentru DSLR Time Lapses: Aveam câteva motoare pas cu pas în jur și voiam cu adevărat să le folosesc pentru a face ceva cool. Am decis că voi face un sistem Pan and Tilt pentru camera mea DSLR, astfel încât să pot crea perioade de timp reci. Elemente de care veți avea nevoie: 2x motoare pas cu pas -htt

IOT123 - SOLAR TRACKER - TILT / PAN, CADRU PANEL, LDR MONTAJ RIG: 9 pași (cu imagini)

IOT123 - SOLAR TRACKER - TILT / PAN, CADRUL PANELULUI, LDR MOUNTS RIG: Majoritatea proiectelor DIY pentru trackere solare cu axa dublă "acolo" se bazează pe 9G Micro Servo, care sunt într-adevăr subevaluate pentru a împinge câteva celule solare, microcontrolerul, bateria și carcasa. Puteți proiecta în jurul

Pan-Tilt Multi Servo Control: 11 pași (cu imagini)

Pan-Tilt Multi Servo Control: În acest tutorial, vom explora cum să controlăm mai multe servos folosind Python pe un Raspberry Pi. Scopul nostru va fi un mecanism PAN / TILT pentru a poziționa o cameră (o PiCam). Aici puteți vedea cum va funcționa proiectul nostru final: Control Servo Control loop loop test:

Pan și Tilt Head controlate de la distanță: 7 pași

Pan Pan și Tilt Head controlat de la distanță: mi-am dorit întotdeauna un pan Pan și Tilt Head controlat de la distanță. Poate că a fost pentru camera mea video, un shooter cu bandă de cauciuc sau un pistol cu apă. Nu contează cu adevărat ce ați pus pe puntea superioară (atâta timp cât nu este prea greu), cu acest mic proiect yo