Cuprins:

- Pasul 1: Funcționarea de către utilizator a secvențialului digital

- Pasul 2: Detalii tehnice

- Pasul 3: Detalii tehnice

- Pasul 4: Separator de ceas cu 7 segmente

- Pasul 5: Divizor de ceas pe minut

- Pasul 6: Pitch Clock Divider

- Pasul 7: Redare / Pauză / Selectare Mașină de stat

- Pasul 8: Redare / Pauză / Selectare Mașină de stat

- Pasul 9: ieșire FSM

- Pasul 10: ieșire FSM

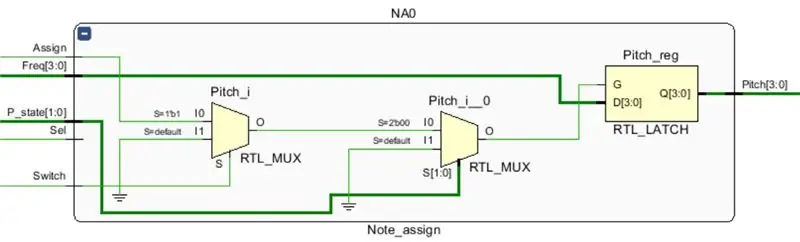

- Pasul 11: Notă Alocare

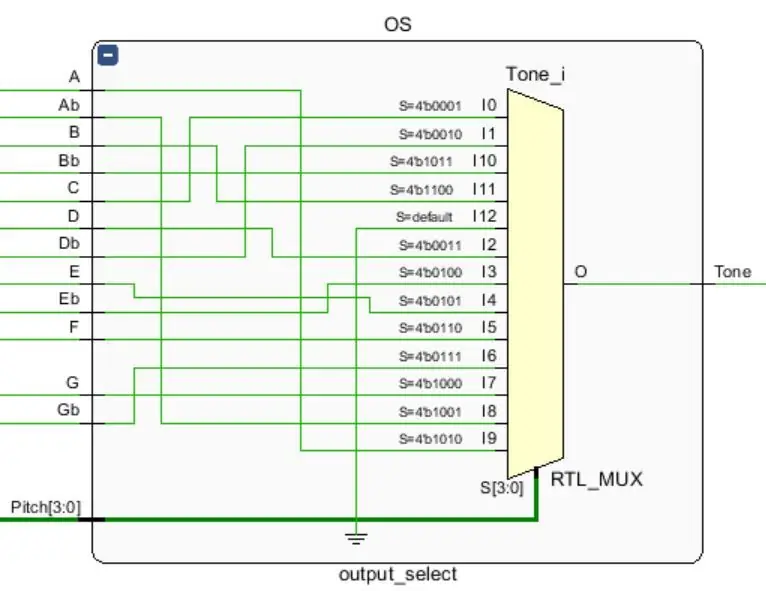

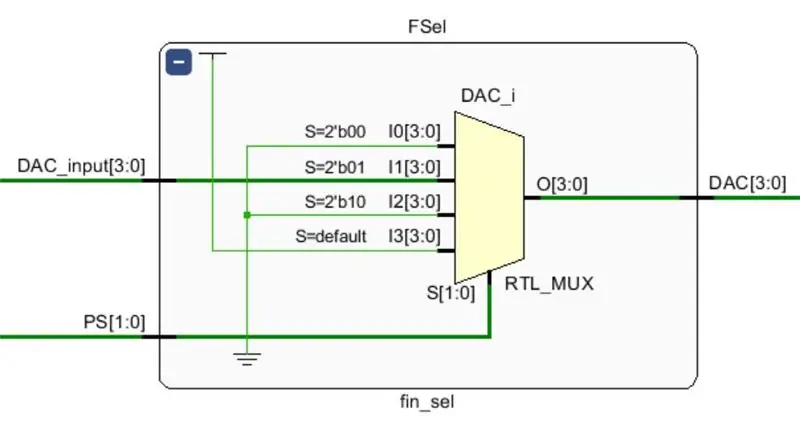

- Pasul 12: Selectare ieșire

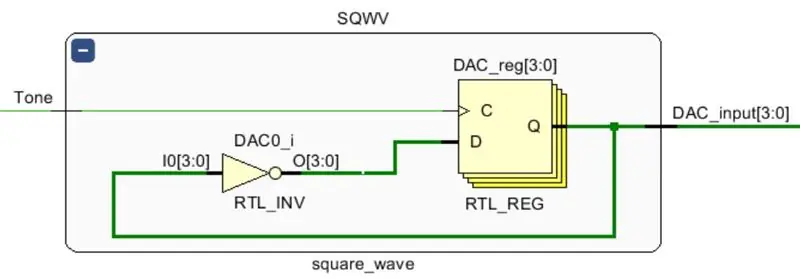

- Pasul 13: Square Wave Gen

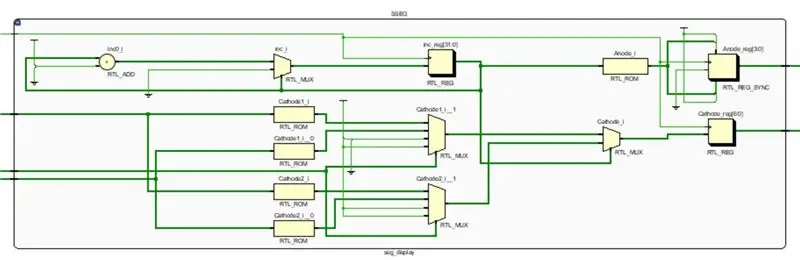

- Pasul 14: afișaj pe 7 segmente

- Pasul 15: Selectare finală

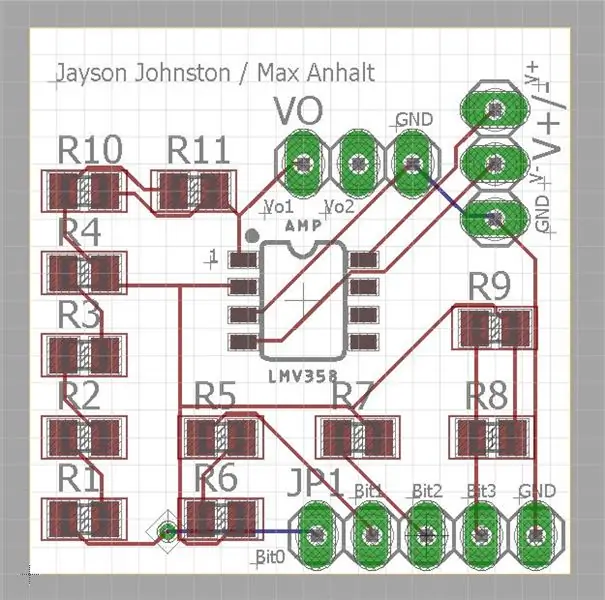

- Pasul 16: Dispozitive externe: DAC

- Pasul 17: Dispozitive externe: Difuzor

- Pasul 18: Demo video

- Pasul 19: Cod VHDL

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:46.

- Modificat ultima dată 2025-01-23 15:04.

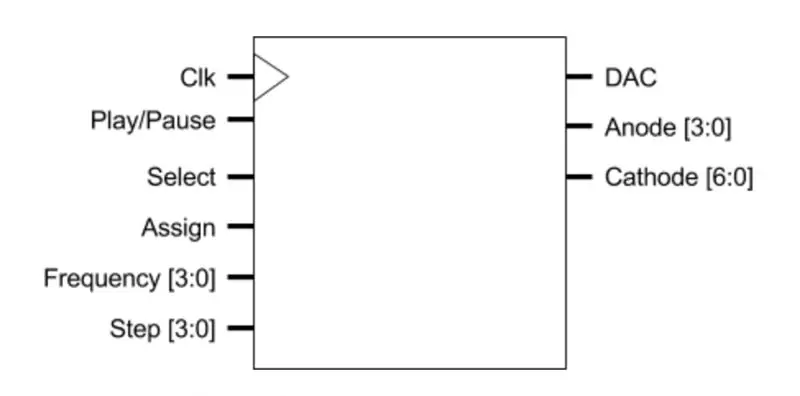

CPE 133, Cal Poly San Luis Obispo

Creatorii de proiecte: Jayson Johnston și Bjorn Nelson

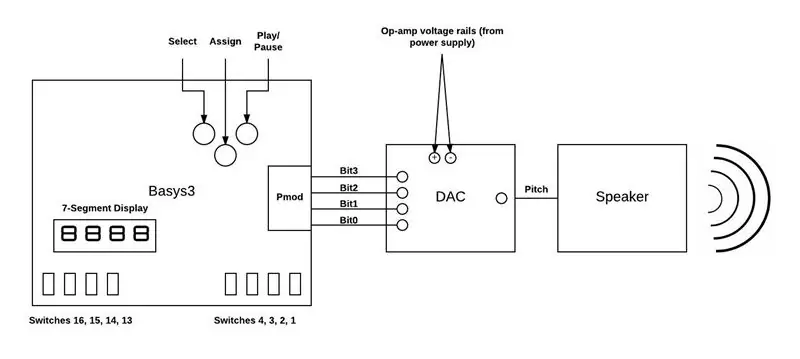

În industria muzicală de astăzi, unul dintre cele mai utilizate „instrumente” este sintetizatorul digital. Fiecare gen de muzică, de la hip-hop la pop și chiar country, folosește un sintetizator digital în studio pentru a crea ritmurile și sunetele de care au nevoie pentru a-și aduce muzica la viață. În acest tutorial, vom crea un sintetizator foarte simplu cu placa Basys 3 FPGA.

Sintetizatorul va putea reda patru note de sfert selectate la un număr constant de bătăi pe minut. Utilizatorii vor utiliza comutatoarele pentru a atribui fiecare notă trimestrială unui ton muzical. Pentru acest proiect, folosim un convertor digital pe analog pe 4 biți (DAC) pentru a prelua ieșirea de pe placă și a o converti într-un semnal analog. Ieșirea din DAC va fi apoi alimentată către un difuzor standard al computerului, creând muzica noastră. Sunt posibile șaisprezece pasuri discrete. Vom restricționa sintetizatorul la o singură octavă de 12 note, care se încadrează între mijlocul C (261,6 Hz) și B4 (493,9 Hz). Utilizatorul va avea, de asemenea, opțiunea de a atribui mai multe note în același timp, precum și de a atribui o odihnă apăsând atribuire, fără a avea niciunul dintre comutatoarele de tonalitate deplasate în sus. Deoarece fiecare notă este selectată și este redată, nota cu litere este afișată pe afișajul cu 7 segmente. Vom folosi, de asemenea, trei dintre butoanele de pe tablă, unul pentru redarea și întreruperea muzicii, unul pentru resetarea sintetizatorului și punerea acestuia în modul „selecție” și al treilea pentru atribuirea fiecărei note un ton în timp ce se află în modul de selecție.

Odată ce utilizatorul este mulțumit de alegerea notelor și după apăsarea butonului de redare, sintetizatorul va reda fiecare notă în mod repetat până când utilizatorul fie apasă pauză, fie selectează.

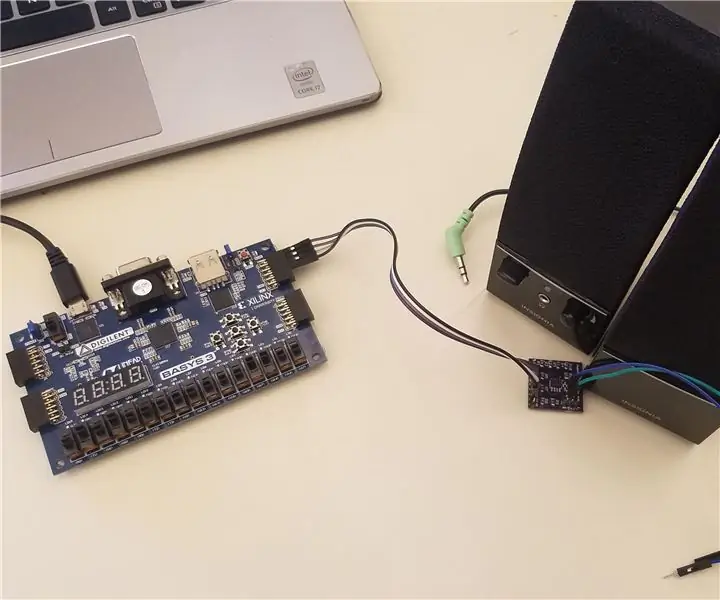

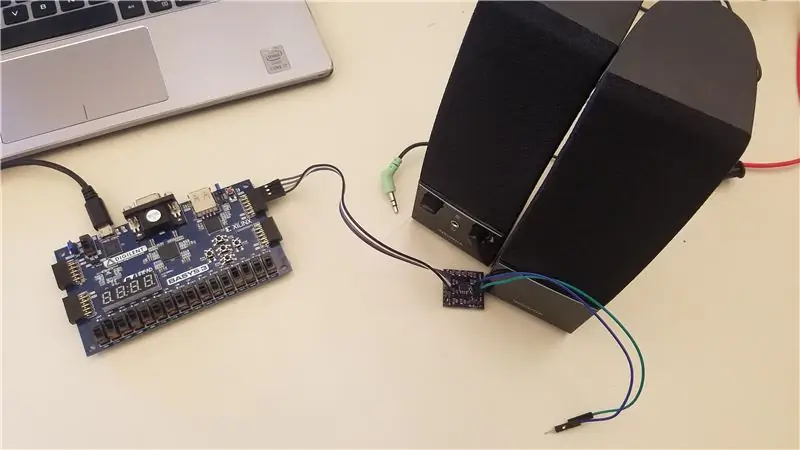

Iată o listă a echipamentului necesar:

- Vivado (sau orice spațiu de lucru VHDL)

- Basys 3 sau o placă FPGA similară

- Convertor digital-analog (min. 4 biți)

- Difuzor cu mufă pentru căști

- Conducte de sârmă

Pasul 1: Funcționarea de către utilizator a secvențialului digital

Următorii pași sunt să acționați secvențialul digital. Secvențialul digital acceptă redarea a 12 tonuri distincte (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), care variază de la 261,6 Hz la 493,9 Hz.

1. Apăsați butonul din stânga pentru a pune placa în modul de selecție. În acest mod, cele 4 comutatoare din stânga (comutatoarele 13-16) vor fi folosite fiecare pentru a stoca o valoare distinctă a pasului.

2. Pentru a face o selecție, întoarceți unul dintre comutatoarele din stânga și apoi utilizați cele 4 comutatoare din dreapta (comutatoarele de la 1 la 4) pentru a alege tonul dorit. Tonul asociat cu o combinație specifică de comutatoare din dreapta va fi afișat pe afișajul de șapte segmente, iar afișajul se va actualiza la noul ton asociat ori de câte ori comutatoarele din dreapta sunt trecute la o nouă combinație. O odihnă poate fi atribuită neatribuind niciodată un ton la unul dintre comutatoarele din stânga sau atribuind un ton prezentat pe afișaj la notă. Odată ce tonul dorit a fost găsit și este afișat pe ecran, apăsați butonul de atribuire inferior pentru a atribui acel ton specific notei.

3. Repetați pasul 2 pentru cele trei note rămase, prin rotirea fiecăruia dintre comutatoarele stânga rămase activate individual, alegând tonalitatea respectivă cu comutatoarele din dreapta și apăsând butonul de jos pentru a atribui tonalitatea notei. Notele multiple pot fi atribuite aceluiași ton prin deplasarea mai multor comutatoare stânga în sus în același timp.

4. Acum că toate tonurile de notă au fost atribuite, secvențialul digital este gata de redare. Pentru a reda notele pe difuzor, pur și simplu apăsați butonul drept de redare / pauză pentru a începe redarea muzicii. Ordinea secvenței de redare reflectă tonurile asociate cu comutatoarele din stânga, de la stânga la dreapta. Notele vor fi redate la un număr stabilit de bătăi pe minut, în ordinea 1, 2, 3, 4, 1, 2…. Afișajul va afișa nota care este redată în prezent pe măsură ce difuzoarele redă muzică. Pentru a întrerupe redarea muzicii, pur și simplu apăsați butonul din dreapta, apoi muzica se va opri din redare și un simbol de pauză va fi afișat pe afișaj. Apăsând din nou butonul din dreapta se va relua redarea.

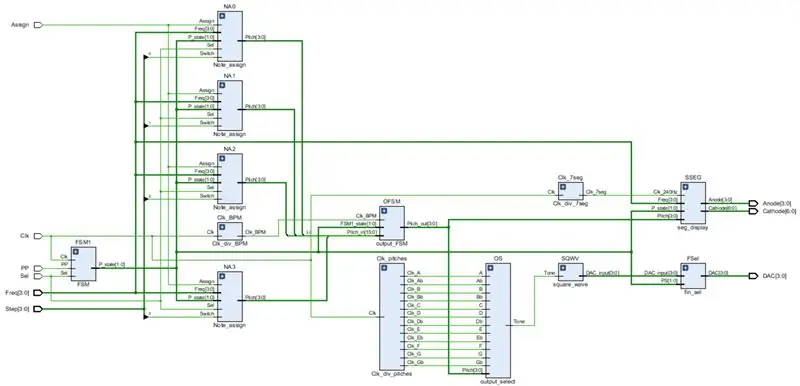

Pasul 2: Detalii tehnice

Sintetizatorul nostru folosește multe componente digitale diferite. Sunt incluse mașinile cu stări finite, registre, multiplexoare, separatoare de ceas și multe altele. Pentru a ne construi sintetizatorul, am folosit 10 fișiere modulare unice. În loc să facem din fiecare modul o componentă, am descompus fișierele modulare în funcție de funcție. Cele mai multe module, ca urmare, sunt mai multe componente. Rețineți că imaginea de mai sus arată fiecare bloc legat împreună în designul nostru de top.

Vom discuta fiecare modul descriind intrările și ieșirile, descompunând componentele sale și explicând scopul său în proiectarea generală. Un fișier ZIP este inclus în partea de jos a instructabilului, care conține fiecare fișier de cod VHDL utilizat în proiect.

Intrări

- Clk (semnal de ceas nativ)

- PP (redare / pauză)

- Sel (pune sintetizatorul în modul de selecție)

- Atribuiți (atribuiți un pas unui pitch)

- Pas (notele de poziție)

- Freq (comutatoarele care creează tonul dorit)

Ieșiri

- Anod (anodi cu 7 segmente)

- Catod (catoduri cu 7 segmente)

- DAC (4 biți care conduc DAC)

Pasul 3: Detalii tehnice

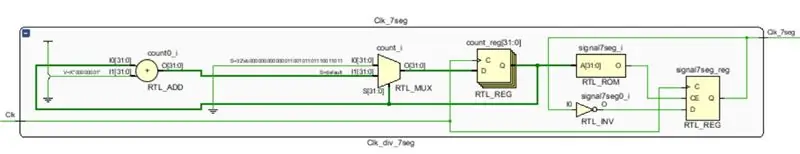

Pasul 4: Separator de ceas cu 7 segmente

Sintetizatorul nostru folosește trei separatoare de ceas, toate producând semnale care au un scop diferit în proiectul nostru. Un divizor de ceas preia un semnal nativ de ceas și produce un semnal modificat care are o frecvență mai mică decât semnalul de ceas original. Ceasul nativ al bazei 3 este de 100 MHz. Aceasta este frecvența pe care o folosesc separatoarele noastre de ceas. Dacă utilizați o placă FPGA diferită cu o frecvență de ceas nativă diferită, poate fi necesar să modificați codul.

Divizorul de ceas cu 7 segmente produce un semnal care conduce fișierul seg_display. Vom explica cum funcționează acest fișier mai detaliat când ajungem la secțiunea sa. În esență, acest divizor de ceas produce un semnal de 240 Hz care va fi utilizat pentru a comuta între anodii și catodii de pe afișaj. Semnalul este de 240 Hz, deoarece frecvența la care ochiul uman nu poate recunoaște absența luminii este de 60 Hz. Folosim două cifre, deci dublând această frecvență, fiecare cifră va oscila la 60 Hz. Apoi îl dublăm pentru a obține 240 Hz, deoarece sistemul se schimbă numai atunci când semnalul crește, nu când scade.

Pentru a realiza acest lucru, divizorul preia semnalul nativ de 100 MHz și se numără pe fiecare margine ascendentă. Când contorul ajunge la 416667, ieșirea va merge de la scăzut la înalt sau invers.

Intrări

Clk (semnal de ceas nativ)

Ieșiri

Clk_7seg (to seg_display)

Componente

- D înregistrare

- MUX

- Invertor

- Sumator

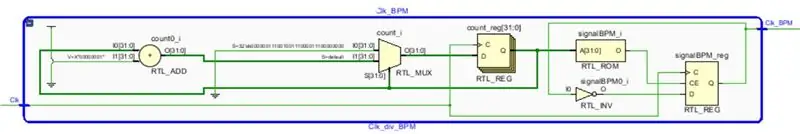

Pasul 5: Divizor de ceas pe minut

Divizorul de ceas BPM funcționează într-un mod similar. Acest divizor produce frecvența ceasului care conduce comutarea între cei patru pași atunci când emite tonuri în starea de redare. Am decis să comutăm între note la 100 BPM. La 100 BPM, fiecare notă va fi redată timp de 3/5 dintr-o secundă. Semnalul rezultat ar avea o frecvență de 1,67 Hz.

Pentru a produce un semnal de această frecvență, am folosit din nou un sistem de numărare, dar de data aceasta numărul a fost de 60 de milioane. De fiecare dată când contorul atingea 60 de milioane, semnalul de ieșire ar comuta în sus sau în jos.

Intrări

Clk (frecvența nativă a ceasului)

Ieșiri

Clk_BPM (către output_FSM)

Componente

- D înregistrare

- MUX

- Invertor

- Sumator

Pasul 6: Pitch Clock Divider

Divizorul de ceas Pitch este cel mai mare dintre divizoarele noastre de ceas. Acest divizor emite 12 semnale diferite corespunzătoare celor 12 note diferite pe care le poate reda sintetizatorul nostru. Folosind cunoștințele de bază ale teoriei muzicale, am dedus că un bit sau un autobuz ar putea oscila la o rată care corespunde frecvenței notelor muzicale. Pentru a vedea frecvențele pe care le-am folosit, uitați-vă aici. Am folosit a patra octavă de pitchuri.

Același sistem de numărare este folosit aici. Pentru valorile specifice pe care le-am numărat, consultați fișierul etichetat Clk_div_pitches.

Intrări

Clk (frecvența nativă a ceasului)

Ieșiri

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (la output_select)

Componente

- D înregistrare

- MUX

- Invertor

- Sumator

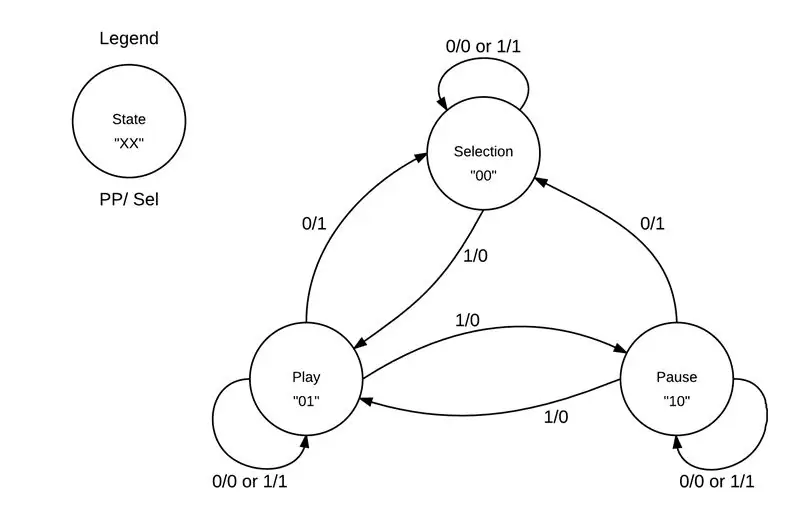

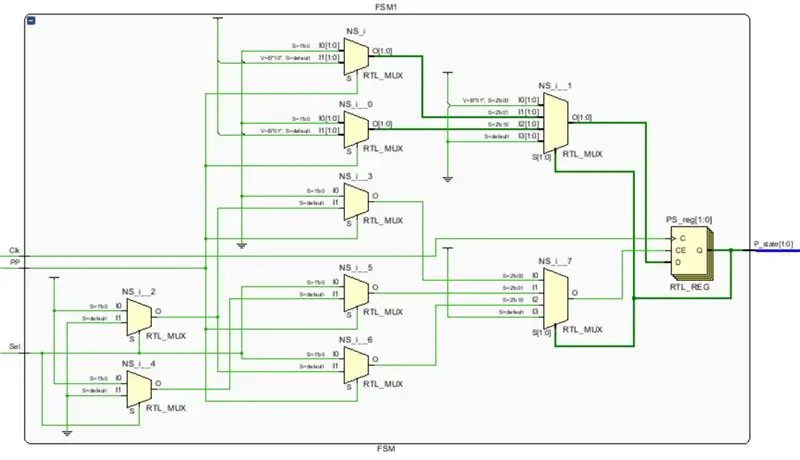

Pasul 7: Redare / Pauză / Selectare Mașină de stat

În proiectul nostru există două mașini cu stare finită (FSM). Un FSM este un dispozitiv logic care poate exista într-o singură stare dintr-o cantitate finită de stări. Folosind un FSM, un circuit digital poate trece la o nouă stare bazată pe o combinație de intrări. Folosind logica de intrare, starea unui FSM se va schimba atunci când există o margine ascendentă a ceasului. Din starea și intrările în circuit, puteți crea logică de ieșire care oferă ieșiri care există numai dacă FSM se află într-o anumită stare.

Mașina de stat PPS este primul FSM din circuitul nostru. Există trei state în acest FSM; Mod redare, pauză și selecție. Pentru a ne deplasa prin diferite stări, am folosit butoanele PP și Selection. Consultați diagrama de stare de mai sus pentru a vedea cum au loc tranzițiile între stări. Am făcut această tranziție FSM pe marginea ascendentă a ceasului nativ de 100 MHz, astfel încât să fie imposibil ca mașina să nu facă tranziție atunci când unul dintre butoane a fost apăsat, chiar și pentru o perioadă foarte scurtă de timp. Starea actuală (P_state) este singura ieșire din acest modul.

Intrări

- Clk (frecvența nativă a ceasului)

- Sel (buton stânga)

- PP (butonul din dreapta)

Ieșiri

P_state (starea actuală, către output_FSM, note_assign, seg_dsiplay, final_select)

Componente

- MUX

- D înregistrare

Pasul 8: Redare / Pauză / Selectare Mașină de stat

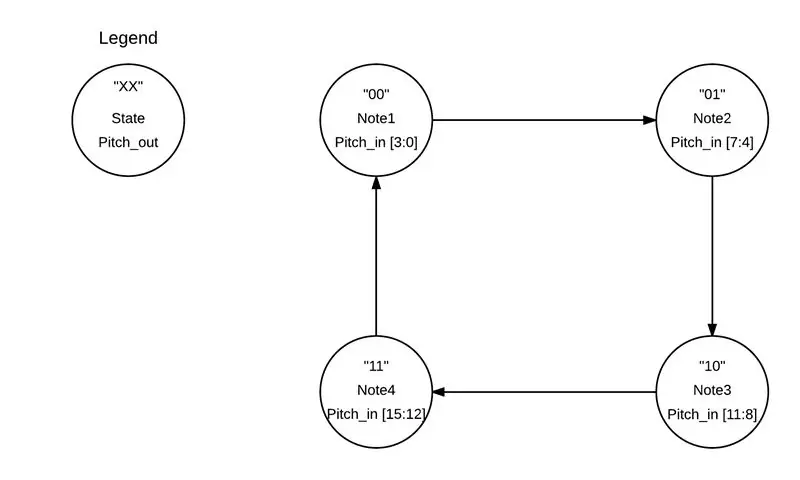

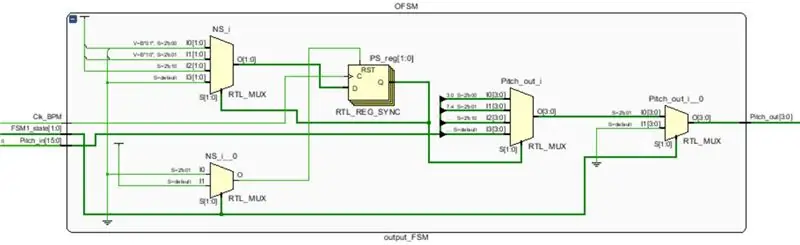

Pasul 9: ieșire FSM

Acesta este al doilea FSM la care se face referire în secțiunea anterioară. Acest FSM îndeplinește o funcție diferită de cealaltă, dar baza pentru aceasta este în esență aceeași.

Ieșirea FSM funcționează numai dacă starea actuală din primul FSM este „01” (starea de redare). În esență, aceasta este activarea pentru modul. Dacă starea este „01”, atunci FSM va comuta între stările de pe marginea ascendentă a semnalului de ceas BPM. Facem acest lucru deoarece output_FSM controlează numărul binar pentru pitch-ul selectat care este trimis către modulele output_select și seg_display. FSM are o intrare de 16 biți provenind de la modulul de atribuire a notelor, care va fi acoperit în continuare. În starea „00” pentru output_FSM, modulul va emite „xxxx” pentru prima notă atribuită. Apoi în „01”, va afișa „aaaa” pentru a doua notă și așa mai departe pentru fiecare notă înainte de a reveni la prima notă. Vezi diagrama de stare de mai sus.

Acest FSM diferă de primul deoarece nu există o logică de intrare pentru a controla comutarea între stări. În schimb, FSM va funcționa numai atunci când starea din primul FSM este „01”, iar apoi acest FSM va trece între state doar pe marginea ascendentă a semnalului de ceas. O altă diferență este că acest modul are logică de ieșire, ceea ce înseamnă că nu generează starea actuală, ci scoate numărul binar pentru pitch în starea respectivă.

Intrări

- Clk_BPM (semnal de ceas BPM de la divizorul de ceas)

- FSM1_state (PS de la PPS FSM)

- Pitch_in (prezentări de la note_assign)

Ieșiri

Pitch_out (un pitch la un moment dat, pentru output_select și seg_display)

Componente

- MUX

- D înregistrare

Pasul 10: ieșire FSM

Pasul 11: Notă Alocare

Modulul de atribuire a notelor este responsabil pentru atribuirea efectivă a unui pitch notei de poziție sau pasului. Acest modul este de fapt destul de simplu. Mai întâi verifică dacă circuitul este în starea de „selecție” și dacă un comutator cu trepte (extrem stânga) este ridicat. Dacă acest lucru este adevărat și butonul de atribuire este apăsat, ieșirea modulului va fi egală cu numărul binar reprezentat de comutatoarele de frecvență (extremă dreapta).

Inițial, am încercat să realizăm un modul care să salveze de fapt unul dintre semnalele de ceas pitch la ieșire, dar am întâmpinat probleme cu schimbarea ieșirii pentru a urma semnalele ceasului de intrare. Acesta este singurul modul utilizat de mai multe ori în proiectarea finală. Fiecare pas are asociat un modul note_assign și, din această cauză, fiecare instanță a modulului primește un bit din magistrala Step.

Intrări

- P_state (starea actuală din PPS FSM)

- Sel (buton stânga)

- Comutator (comutator cu un singur pas)

- Freq (comutatoare pentru extrema dreapta)

- Alocare (butonul de jos, atribuie o notă)

Ieșiri

Pitch (număr binar, la output_FSM)

Componente

- MUX

- D înscrieți-vă

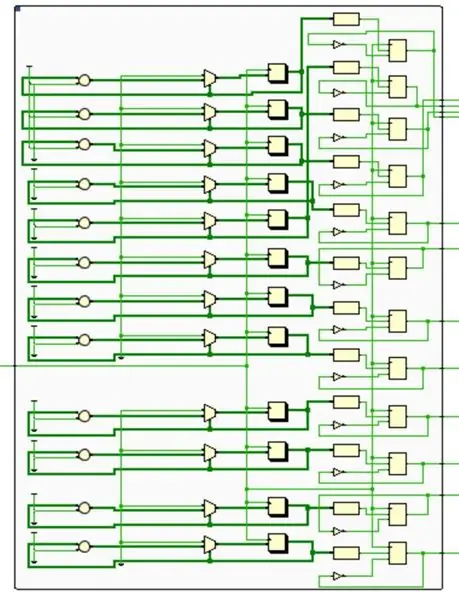

Pasul 12: Selectare ieșire

Selectarea ieșirii este responsabilă pentru preluarea numărului binar pentru un pitch și conectarea acestuia la semnalul de ceas respectiv. În ciuda dimensiunilor sale, acesta este, de asemenea, un modul relativ simplu. Output_select este în esență un decodor binar, decodificând numărul binar pentru un pitch la un semnal de ceas specific. De fapt, atribuirea ieșirii la o frecvență de ceas a funcționat mai bine aici în comparație cu modulul note_assign, deoarece tot acest modul a trebuit să facă a fost MUX semnalele de ceas cu numărul binar reprezentând intrarea de control.

Ne cerem scuze pentru rutarea ciudată, Vivado a organizat semnalele de pitch în ordine alfabetică pentru fișierul clk_div_pitches, dar pentru acest fișier le-a organizat prin creșterea numărului binar, determinând pitchurile să fie într-o ordine diferită. De asemenea, rețineți că dacă numărul binar de la output_FSM a fost „0000” sau ceva mai mare decât „1100”, atunci MUX a trimis printr-un semnal plat „0”.

Intrare

- Pitch (din output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (semnale de ceas pitch)

Ieșire

Tone (un singur bit care se potrivește cu semnalul de ceas selectat, la square_wave)

Componente

MUX

Pasul 13: Square Wave Gen

Modulul square_wave este generatorul pentru unda pătrată care este trimisă de la placă la DAC. Folosind semnalul de ton din fișierul anterior, această pătrat_undă inversează numărul de 4 biți între „0000” și „1111” pe marginea ascendentă a tonului. Tonul este o frecvență specifică, astfel încât square_wave produce o undă cu o frecvență diferită atunci când output_FSM trece la o altă stare. Ieșirea de 4 biți din acest modul merge la modulul fin_sel, unde logica dictează dacă această magistrală va fi transmisă pe baza stării din PPS FSM.

O alternativă la acest generator de unde pătrate este producerea unei unde sinusoidale. Deși acest lucru ar produce cel mai probabil un ton final mai bun, este considerabil mai dificil de implementat, așa că am optat doar pentru a genera un val pătrat.

Intrări

Ton (bit oscilant din output_select)

Ieșiri

DAC_input (magistrală oscilantă pe 4 biți care se schimbă la aceeași frecvență a tonului)

Componente

- Invertor

- D înregistrare

Pasul 14: afișaj pe 7 segmente

Modulul seg_display controlează afișajul cu 7 segmente de pe placa noastră de bază. În cadrul modulului, au loc două procese. Primul proces decodifică Freq când se află în starea de „selecție” sau Pitch când se află în modul „play”. În modul „pauză”, modulul decodează pentru a afișa simbolul pauză. Privind codul VHDL, puteți vedea că decodorul binar decodează de fapt intrarea în două semnale diferite, catodul1 și catodul2. Catodul 1 reprezintă litera corespunzătoare tonului care trebuie afișat, iar catodul 2 reprezintă simbolul plat (b) dacă există unul. Motivul pentru aceasta se referă la al doilea proces realizat de modulul seg_display.

Pe o placă basys3, afișajul segmentului are catoduri comune. În timp ce anodii controlează care cifră este pornită, catodii controlează ce segmente sunt activate. Deoarece afișajul are catoduri comune, asta înseamnă că puteți afișa un singur set de segmente odată. Acest lucru pune o problemă pentru acest proiect, deoarece dorim să afișăm o literă în prima cifră și simbolul plat, dacă este necesar, în același timp. Acum îți amintești semnalul de ceas 7seg? Pentru a rezolva această problemă, schimbăm anodii și catodii înainte și înapoi pe semnalul de ceas 7seg. Deoarece semnalul ceasului este de 240 Hz și folosim două cifre, fiecare cifră va oscila la 60 Hz. Pentru ochiul uman, va părea că cifrele nu oscilează deloc.

De asemenea, rețineți că afișajul plăcii basys3 utilizează logică negativă. Aceasta înseamnă dacă un anod sau catod este setat la '0', cifra sau segmentul respectiv va fi activat și invers.

Intrări

- Pitch (număr binar pentru o notă, utilizat în starea de joc)

- Freq (comutatoare de frecvență, utilizate când se află în stare de selecție)

- P_state (starea actuală din PPS FSM)

- Clk_240Hz (semnal de ceas de la Clk_div_7seg, dublu 120 pentru că folosim doar marginea ascendentă)

Ieșiri

- Catod (magistrală care controlează segmente de pe afișaj, ieșire finală)

- Anod (magistrală care controlează cifrele de pe afișaj, ieșire finală)

Componente

- Zăvor

- MUX

- D înregistrare

Pasul 15: Selectare finală

Selecția finală este ultimul modul utilizat în acest proiect. Un alt modul simplu, acest modul controlează ieșirea finală care va merge la DAC. Când se află în starea „selecție” sau „pauză”, modulul va emite un „0000” static, astfel încât să nu fie redată muzică din difuzoare. În starea „redare”, modulul va emite 4 biți oscilanți, așa cum este determinat de square_wave.

Intrări

- P_state (starea actuală din PPS FSM)

- DAC_input (oscilantul de 4 biți din square_wave)

Ieșiri

DAC (este egal cu DAC_input în starea de joc, ieșire finală)

Componente

MUX

Pasul 16: Dispozitive externe: DAC

Un convertor digital-analog (DAC) preia un semnal discret și îl convertește într-un semnal continuu. DAC-ul nostru are patru biți și este fabricat dintr-un amplificator sumator. Folosind un raport de rezistențe în bucla de alimentare și feedback, am reușit să creăm un sistem care produce ieșiri la 16 niveluri diferite creând prin „însumarea” fiecărei ramuri. Bit0, ramura superioară, are cea mai mică greutate și contribuie cu cel mai mic potențial atunci când este ridicat, datorită rezistenței mai mari a ramurilor. Greutatea crește pe măsură ce coborâți pe ramuri. Dacă ar fi să numărați în binar în sus și apoi înapoi în jos folosind intrările de biți, tensiunile de ieșire ar arăta ca o undă sinusoidală. Intrarea în DAC a fost conectată la cea a PMOD-urilor de pe placă pentru a transfera semnalul de 4 biți.

DAC a fost inițial asamblat pentru o clasă de inginerie electrică și a fost proiectat și lipit de noi, nu cumpărat de la un magazin. Mai sus este o imagine a fișierului de proiectare pentru crearea plăcii cu circuite imprimate.

Pasul 17: Dispozitive externe: Difuzor

Pentru acest proiect, nu veți dori să cumpărați o pereche de boxe super drăguță. După cum vă puteți da seama, sunetul este destul de simplu. Am mers și am cumpărat un set de difuzoare de 8 USD de la Best Buy. Orice lucru cu o mufă pentru căști funcționează bine. Monotona funcționează bine. Puteți folosi chiar și căști, dar s-ar putea să le aruncați!

Pentru a conecta ieșirea DAC la difuzoare, am folosit cabluri jumper și apoi am ținut cablul de ieșire la vârful mufei pentru căști și cablul pentru împământare la bază. Am încercat să folosim bandă electrică pentru a ține cablurile în poziție, dar a cauzat multe interferențe. Încercarea unui alt stil de bandă ar putea rezolva această problemă.

Pentru difuzoarele noastre, le-am orientat către cea mai înaltă setare și am obținut un zgomot decent.

Și acesta este ultimul pas pentru crearea unui secvențiator digital de pe o placă FPGA! Accesați următoarele două secțiuni pentru a descărca tot codul nostru VHDL și a vedea secvențierul în acțiune.

Pasul 18: Demo video

Acest videoclip prezintă versiunea finală a proiectului de lucru, inclusiv procesul de atribuire a comutatoarelor la 4 tonuri distincte, iar difuzoarele redau notele respective.

Pasul 19: Cod VHDL

Iată codul pentru întregul proiect, inclusiv constrângerea și fișierele SIM utilizate la construirea secvențierului. Rețineți că fișierele de design neutilizate spun acest lucru în arhitectură.

Recomandat:

Dimmer digital AC puternic folosind STM32: 15 pași (cu imagini)

Dimmer digital puternic de curent alternativ care utilizează STM32: De Hesam Moshiri, hesam.moshiri@gmail.com încărcări de AC trăiesc cu noi! Pentru că sunt peste tot în jurul nostru și cel puțin aparatele electrocasnice sunt alimentate cu curent. Multe tipuri de echipamente industriale sunt, de asemenea, alimentate cu monofazat de 220V-AC

Adăugați un afișaj digital la un receptor de comunicații vechi: 6 pași (cu imagini)

Adăugați un afișaj digital la un receptor de comunicații vechi: una dintre deficiențele utilizării unui echipament de comunicații mai vechi este faptul că discul analogic nu este foarte precis. Întotdeauna ghiciți frecvența pe care o primiți. În benzile AM sau FM, în general, aceasta nu este o problemă, deoarece de obicei

Cum să dărâmați un etrier digital și cum funcționează un etrier digital: 4 pași

Cum să dărâmiți un etrier digital și cum funcționează un etrier digital: Mulți oameni știu cum să folosească etrierele pentru măsurare. Acest tutorial vă va învăța cum să dărâmați un etrier digital și o explicație a modului în care funcționează etrierul digital

Cum să dezasamblați un computer cu pași și imagini ușoare: 13 pași (cu imagini)

Cum să dezasamblați un computer cu pași și imagini ușoare: Aceasta este o instrucțiune despre cum să dezasamblați un computer. Majoritatea componentelor de bază sunt modulare și ușor de îndepărtat. Cu toate acestea, este important să fiți organizat în acest sens. Acest lucru vă va ajuta să nu vă pierdeți piese și, de asemenea, să faceți reasamblarea

Vizualizator digital de imagini 3D - „The DigiStereopticon”: 6 pași (cu imagini)

Vizualizator digital de imagini 3D - „The DigiStereopticon”: fotografia stereoscopică a căzut în lipsă. Acest lucru se datorează probabil faptului că oamenilor nu le place să poarte ochelari speciali pentru a vedea instantanee de familie. Iată un mic proiect distractiv pe care îl poți face în mai puțin de o zi pentru a-ți face imaginea 3D